# A Low-Power CMOS Optical Communication Front-End Using a Three-Stage TIA for 5Gb/s Applications

# Soorena Zohoori<sup>1</sup>, Mehdi Dolatshahi<sup>2</sup>

1,2- Department of Electrical Engineering, Najafabad Branch, Islamic Azad University, Najafabad, Iran. Email: Dolatshahi@iaun.ac.ir(Corresponding Author)

Received: January 2017 Revised: July 2017 Accepted: July 2017

#### **ABSTRACT:**

In this paper, an optical communication receiver system for 5Gbps applications is proposed concerning power consumption. An inductor-less circuit in three-stages is proposed as the trans-impedance amplifier (TIA), which benefits from the inherent low input resistance of a common gate topology as the first stage. By forming two zeros in this TIA, proper frequency response is obtained while the DC current is reduced. In order to obtain extra gain for the receiver system, three stages of conventional limiting amplifier (LA) are used. In order to verify the circuit performance, the proposed receiver is simulated in HSPICE using 90nm CMOS technology parameters. The receiver is mathematically studied and is matched with the simulations. This paper conducts the simulations, such as eyediagram, noise analysis and fabrication process analysis (Monte-Carlo). The proposed Trans-Impedance Amplifier shows 53.9db $\Omega$  gain, 3.5GHz bandwidth, 15.2pA/ $\sqrt{Hz}$  and only 1.52mw power consumption for 1.2v supply voltage, and the receiver system shows 90.9db $\Omega$ , 3.5GHz bandwidth and 6.34mw power consumption (for 2 stages of TIA and 3 stages of LA) for 1.2v supply voltage. Results indicate that the proposed receiver is suitable to work as a low-power 5Gbps optical communication receiver system.

**KEYWORDS**: Low Power, Trans-impedance Amplifier, Limiting Amplifier, Optical Receiver.

#### 1. INTRODUCTION

Nowadays, optical communication systems have become more and more important and useful. Optical communications between chips, among PCBs and inside the chips are examples of applications for these systems. It is suitable to use optics for transmitting data, whenever the transmission rate is more than Gigabits per second.

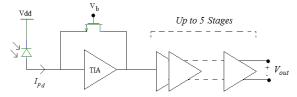

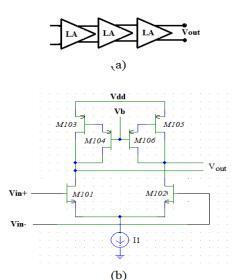

In receiver systems photons are converted to electrons. The photodiode receives the optical signals and produces current signal proportional to density of the received light. The produced current, of course, may be as weak as a few tens of micro amperes [1]. That is why beside a photodiode, a receiver system consists of a TIA stage and up to 5stges of LAs is used to obtain proper domain and swing for digital blocks, as in figure (1).

**Fig. 1.** Block diagram of a typical optical communication receiver

The TIA stage converts and amplifies the input current to voltage, and LA stage provides extra gain. These kinds of receiver systems are implemented in different technologies such as SiGe, BiCMOS, CMOS, GaAs and bipolar [1-3].

Whenever using CMOS technologies, several considered might be noticed. First of all, TIA and LA stages are supposed to operate at high speed applications. Second, the large photodiode parasitic capacitance creates dominant pole at the input node, which needs to be compensated. Third, the output current should be large enough to drive  $50\Omega$  load. On the other side, there are several methods to design high speed circuits such as inductive peaking, shunt peaking and series peaking technique [4-6],  $f_T$  doubler [1], active feed-back [7], 3D inductor serial peaking [8] and slew boosting [9]. Although the above mentioned methods have some superiors, they may have some disadvantages. For example, using inductors in circuits occupies a large area and  $f_T$ -doubler technique doubles the power consumptions in the circuit. In another hand, there are several techniques to reduce the effect of the input capacitance, for instance Regulated cascade (RGC) configuration [10-12,19] and T-coil inductor matching [13]. Regulated cascade configuration has

#### Majlesi Journal of Electrical Engineering

great effect on enlarging the bandwidth, but it is difficult to implement at a low supply voltage [14]. The T-coil inductor matching technique uses inductor coupling to increase the bandwidth and gain in cost of occupying larger area [15].

In this paper, the focus is on obtaining a low power receiver. Challenges are considered to decrease the power consumption while proper bandwidth and gain can be obtained. This is obtained by forming two zeros in the transfer function of the TIA and at each stage of LAs. Hence, the proper frequency response is obtained by consuming less DC current with less power consumption. Besides that, in order to occupy minimum chip area, the proposed receiver is fully designed with transistors (only one resistance is used) and no inductor is used. The proposed circuit is mathematically studied and several analyses are done in order to prove the proper performance of the proposed receiver and the quality of the output signal.

This paper is organized as follows: In section 2 the proposed TIA is given, mathematically discussed and required simulations are done. In section 3, the LA stage is analyzed. In section 4 the receiver system is discussed and finally, conclusion results are given in section 5.

# 2. TIA STAGE

### 2.1. The Proposed TIA

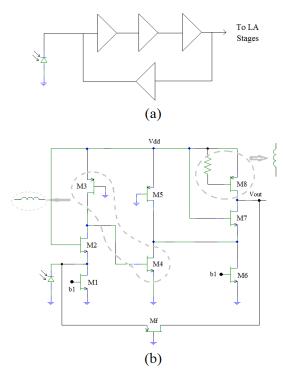

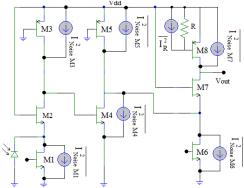

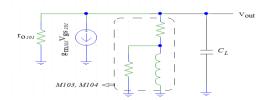

Figure (2) shows the proposed TIA circuit, and figure (3) shows its open loop equivalent circuit. As it can be seen, in order to obtain proper trans-impedance, gain from the TIA stage, 3 stages of amplifiers are connected in series.

M1 and M6 are operating at their saturation region in order to provide proper dc bias current. M2 and M7 complete common gate topology, while M4 completes common source topology. Trans-impedance gain is mostly obtained from this common source structure (M4). Combination of M8 and the resistance provides an active inductive peaking technique (as it is shown in small signal model in figure (3)) which creates a zero in the transfer function at output node, and combination of  $r_{o3}$  at the gate of M4 creates another zero at the drain of M4. These active inductors resonate with the capacitances seen at the output node and drain of M4, respectively and move the poles at these nodes to higher frequencies. Therefore, the effect of parasitic

and load capacitance decreases, and hence increases the bandwidth of the TIA. Using these combinations at these two nodes, allows us to decrease the DC current, while proper bit-rate is obtained. Accordingly, a low-power TIA structure is achieved.

The dominant pole is formed due to parasitic capacitance of photodiode at input node; and to make it go farther from the origin, the input resistance should be reduced. For this, a common gate stage is used at input node for amplifying the signal. Considering M1 operating as an ideal current source and  $r_{02} \rightarrow \infty$ , the input resistance of the circuit can approximately be written as follows:

$$R_{in} \approx \frac{1}{g_{m2} + g_{mb2}} \tag{1}$$

In which,  $g_m$  represents the trans-conductance. This shows quite a small value for input resistance. So far, poles at each three stage in the TIA are compensated.

Fig.2. a) Block diagram.0m b) Proposed TIA circuit

Fig.3. Small signal equivalent circuit of the proposed TIA

So, for the input pole it is possible to write:

$$S_{P,in} = -\frac{g_{m2} + g_{mb2}}{c_{in}} \tag{2}$$

In which C<sub>in</sub> is as follows:

$$C_{in} = C_{pd} + C_{gd1} + C_{gs2} + C_{sb2} \approx C_{pd}$$

(3)

Where  $C_{pd}$  is the parasitic capacitance of photodiode,  $C_{gd}$  is the gate-drain capacitance,  $C_{gs}$  is the gate-source capacitance and  $C_{sb}$  is the source-bulk capacitance.

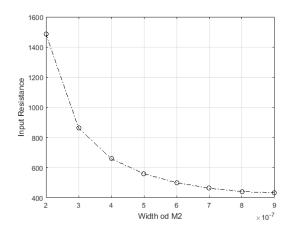

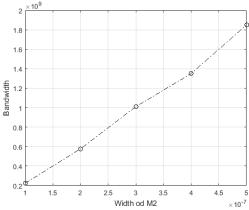

By increasing the trans-conductance of M2, the dominant pole can be moved far away from the origin, and hence proper bandwidth can be obtained. The effect of M2 on input resistance and bandwidth are shown in figure (8) and (9), respectively.

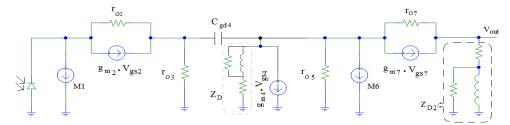

Also, open loop trans-impedance gain of the proposed TIA, which consists of two common gate stages and a common source stage, is as follows:

$$A_V = A_{v,Common\ Gate1} \times A_{v,Common\ Source} \times A_{v,Common\ Gate2}$$

$$A_{v,CommonGate1} = \frac{(g_{m2} + g_{mb2}) \times r_{o3}}{(g_{m2} + g_{mb2} + C_{in}.S) \times (r_{o3}.C_{out1}.S + 1)}$$

$$A_{v,CommonSource} = -g_{m4} \times r_{o5}$$

$$A_{v,CommonGate2} = \frac{(g_{m7} + g_{mb7}) \times Z_{D2}}{(g_{m7} + g_{mb7} + C_{in3}.S) \times (Z_{D2}.C_{out}.S + 1)}$$

(4)

Where,  $C_{out1}$  is the capacitance seen at drain of M2,  $C_{in3}$  is the capacitance seen at source M7 and  $C_{out}$  is the output parasitic capacitance (poles for common source stage are negligible), and we also have:

$$Z_{D2} = \frac{R.C_{gs8}.S + 1}{g_{m8} + C_{gs8}.S} \tag{5}$$

Equation (4), proves that by increasing transconductance of M2, M4 and M7, more gain can be obtained, it also reveals that proper amount of transimpedance gain of TIA mostly depends on the quantity of trans-conductance of M4 and  $r_{O5}$ .

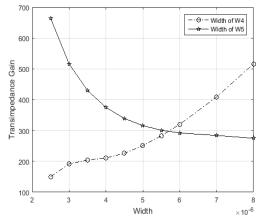

Effect of trans-conductance of M4 and  $r_{O5}$  on transimpedance gain is shown in figure (10). Equation (5), clearly depicts the effect of active inductive peaking in figure (3) at output node. Output resistance at low-frequencies can be written as follows:

$$R_{out} = \frac{r_{07}.r_{06}.(g_{m7} + g_{mb7})}{g_{m8}.(g_{m7} + g_{mb7})r_{07}.r_{06} + 1} \approx \frac{1}{g_{m8}}$$

(6)

And at high frequencies, it can be written as equation (7):

$$\begin{split} Z_{out} &= \\ &\frac{C_{gs8.R.r_{o7}.r_{o6}}(g_{m7} + g_{mb7}).S + r_{o7}.r_{o6}(g_{m7} + g_{mb7})}{C_{gs8}\left(R + r_{o7}.r_{o6}(g_{m7} + g_{mb7})\right).S + g_{m8}.(g_{m7} + g_{mb7})r_{o7}.r_{o6} + 1} \end{split} \tag{7}$$

So, by considering the above mentioned equations, the output pole can be represents as equation (8):

$$S_{p,out} = -\frac{1}{C_{out} \cdot R_{out}} \tag{8}$$

Where,  $C_{out} = C_{dg7} + C_{db7} + C_{dg8} + C_{db8}$  and  $R_{out}$  is the output resistance. Also, by knowing the fact that the dominant pole is formed at input  $node(C_{in} \gg C_{out} \rightarrow S_{p,in} \ll S_{p,out})$ ,  $f_{-3db}$  can approximately be written as equation (9):

$$f_{-3db} \approx \frac{g_{m2} + g_{mb2}}{2\pi . c_{in}} \tag{9}$$

It is clearly revealed that by increasing the transconductance of M2  $(g_{\rm m2})$ , as it is depicted in next section, the input impedance is lessened, and the bandwidth is enlarged.

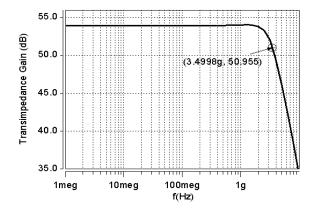

# 3. SIMULATION RESULTS

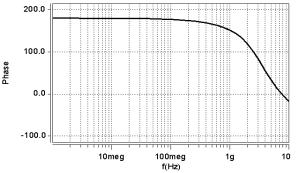

In order to verify the circuit performance, the proposed TIA is simulated in HSPICE using 90nm CMOS technology parameters. Figure (4) shows the frequency response and phase of the proposed TIA. As it can be seen in figure (4), the proposed TIA shows  $53.9 dB\Omega$  trans-impedance gain, 3.5 GHz bandwidth and a proper phase margin. Also, power dissipation for this circuit is 1.52 mw for 1.2 v supply voltage.

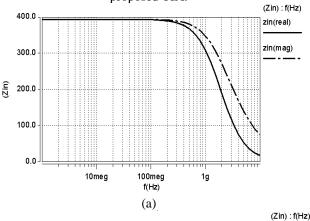

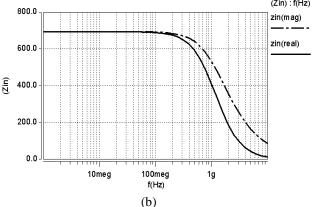

As it was important to study the input resistance and its effect on bandwidth, figure (5) shows the simulated input resistance and input impedance according to frequency variation. As it can be seen, input resistance at -3db frequency is less than  $90\Omega$ , and the input impedance at -3db frequency is less than  $190\Omega$ . This low range of resistance and impedance is due to the use of feedback network and also common gate topology at input node.

**Fig. 4.** (a) Frequency response (b) Phase of the proposed TIA.

**Fig. 5.** Input impedance and input resistance (a) with feedback (b) without feedback network.

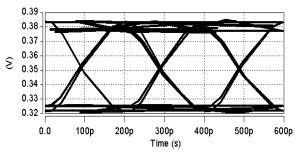

In order to study the impact of noise and intersymbol interference (ISI) and the output signal quality of the proposed TIA, figure (6) shows the simulated eye-diagram of the proposed circuit for  $100\mu A$  5Gbps NRZ PRBS7. The vertical large opening of the eye in figure (6) reveals the low range of bit error rate (BER), and horizontal opening relates the jitter and the sensitivity. Generally, it can be said that wider the opening of the eye, the larger the bandwidth. The eye is opened to about 60mv for an input current of  $100\mu A$ .

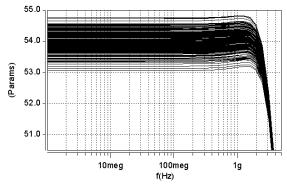

Also, in order to analyze the proposed TIA at fabrication process, Monte-Carlo analysis is done in HSPICE for 200 runs. Figure (7) shows the Monte-Carlo analysis of the proposed TIA. As it can be seen, trans-impedance variation in the fabrication process can be from 53dB up to 54.8dB.

Fig. 6. Simulated Eye-Diagram of the Proposed TIA for 100µA 5Gbps NRZ PRBS7

Fig. 7. Monte-Carlo analysis for 200 runs

In following, effect of width of M2 on input resistance according to equation (1) is analyzed and is shown in figure (8). Also effect of width of M2 on -3dB frequency is analyzed according to equation (9). Moreover, the effect of M4 and M5 width on gain of the TIA according to equation (4) is shown in table III, table IV and figure (10).

Fig. 8. Width of M2 vs. input resistance

**Table 1.** Effect of width of M2 on input resistance according to equation (1)

| `   | 200nm        | 300nm | 400nm | 500nm | 600nm | 700nm | 800nm | 900nm       |

|-----|--------------|-------|-------|-------|-------|-------|-------|-------------|

| Rin | $1487\Omega$ | 862Ω  | 659Ω  | 559Ω  | 500Ω  | 463Ω  | 441Ω  | $432\Omega$ |

**Table 2.** Effect of width of M2 on -3dB frequency according to equation (9)

| W2         | 100nm     | 20nm      | 300nm   | 400nm   | 500nm   | 600nm   |

|------------|-----------|-----------|---------|---------|---------|---------|

| $f_{-3dB}$ | 223Meg.Hz | 577Meg.Hz | 1.01GHz | 1.35GHz | 1.85GHz | 3.46GHz |

**Table 3.** Effect of width of M4 on Trans-impedance gain according to equation (4)

| W4   | 2.5µm | 3µm  | 3.5µm | 4µm  | 4.5µm | 5µm  | 5.5µm | 6µт  | 7μm  | 8µm  |

|------|-------|------|-------|------|-------|------|-------|------|------|------|

| Gain | 150Ω  | 192Ω | 204Ω  | 211Ω | 226Ω  | 251Ω | 283Ω  | 320Ω | 409Ω | 516Ω |

Table 4. Effect of width of M5 on Trans-impedance gain according to equation (4)

| W5   | 2.5µm | 3µm  | 3.5µm | 4µm  | 4.5µm | 5µm  | 5.5µm | бμт  | 7µm  | 8µm  |

|------|-------|------|-------|------|-------|------|-------|------|------|------|

| Gain | 664Ω  | 516Ω | 430Ω  | 375Ω | 339Ω  | 316Ω | 301Ω  | 292Ω | 284Ω | 275Ω |

Fig. 9. Width of M2 vs. bandwidth

Fig. 10. Width of M5 and M4 vs. gain

### 4. NOISE ANALYSIS

Although thermal noise of the TIA stage can be reduced by common mode rejection parameter in LA stages, it is instructive to study the thermal noise of the proposed TIA.

Representing the thermal noise of each transistor by current source, figure (11) shows the equivalent thermal noise of the proposed TIA.

At the first stage of the TIA in the common gate structure, all  $\overline{I_{n,M1}^2}$  flows through  $M_3$  and no part of  $\overline{I_{n,M2}^2}$  flows through M3 [1]. So, M2 actually produces no thermal noise in the circuit. The thermal noise of the first stage (common gate stage) at drain of M2 is according to equation (10):

$$\overline{V_{n,1st \, stage}^2} = \left(\overline{I_{n,M1}^2} + \overline{I_{n,M3}^2}\right) \times r_{o3}^2$$

(10)

Fig. 11. Equivalent noise circuit

Dividing this quantity by the trans-impedance gain of  $A_{V1}$  yields the input referred noise of the first stage, which is equal to equation (11):

$$\overline{I_{n,1st \ stage}^2} = \overline{I_{n,M1}^2} + \overline{I_{n,M3}^2}$$

(11)

Equation (11), suggests that the noise current of M1 and M3 are referred to the input node with a unity factor.

For the second stage, that is the common source stage, representing noise of M4 and M5 by the current sources in figure (8), the thermal noise at drain of M4 can be written as equation (12):

$$\overline{V_{n,2nd \, stage}^2} = 4KT\gamma (g_{m4} + g_{m5}) \times (r_{04} || r_{05})^2$$

(12)

In which K is the Boltzmann constant and T is temperature. Dividing equation (12) by gain of first and second stage, the input referred noise of this stage can be as equation (13):

$$\overline{I_{ln,2nd \, stage}^{2}} = \frac{\overline{V_{n,2nd \, stage}^{2}}}{[g_{m4}. (r_{04} || r_{05})]^{2}} \times \frac{1}{\overline{A_{V.1st \, stage}^{2}}}$$

$$= 4KT\gamma \cdot \left(\frac{1}{g_{m4}} + \frac{g_{m5}}{g_{m4}^2}\right) \times \frac{1}{A_{V.1st\,stage}^2}$$

(13)

In which  $\gamma$  is the coefficient factor.

For the third stage, similar to the first stage, all  $\overline{I_{n,M6}^2}$  flows through  $Z_{D2}$  and no part of  $\overline{I_{n,M7}^2}$  flows through  $Z_{D2}$ . By considering this at the output node we have equation (14):

$$\overline{V_{n,3rd\,stage}^2} = \left(\overline{I_{n,M6}^2} + \overline{I_{n,ZD2}^2}\right) \times Z_{D2}^2 \tag{14}$$

And the input referred noise of this stage can be written as equation (15):

$$\overline{I_{in,3rd\ stage}^{2}} = \frac{\overline{I_{n,M6}^{2} + \overline{I_{n,ZD2}^{2}}}}{\left(A_{V,1st\ stage} + A_{V,2nd\ stage}\right)^{2}}$$

(15)

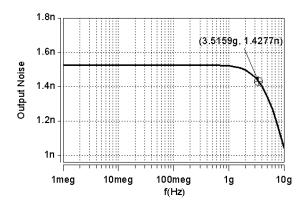

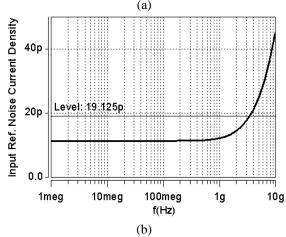

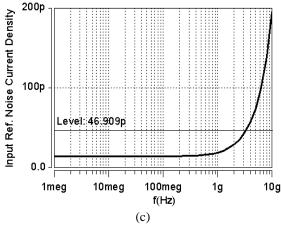

In order to verify the noise behavior of the proposed TIA, noise analysis is done in HSPICE. Figure (12) shows the simulated output and input referred noise of the proposed TIA, respectively. As it can be seen, the feedback network has reduced the input referred thermal noise at  $f_{-3dB}$  from 46.9p to 19.1p.

**Fig. 12**. (a) Output noise (b) Input referred noise of the proposed TIA. (c) Input referred noise of the TIA without feedback system.

### 5. LA STAGE

In order to achieve a proper gain for the receiver system, three stages of a conventional limiting amplifier (LA) is used in this work. Figure (13-a) shows the LA stage building block and figure (13-b) shows the structure of each cell gain.

As shown in figure (13), three differential stages are used as LA stages, with active inductive peaking technique as their loads. The equivalent circuit is shown in figure (14). By using half circuit, gain of each stage can be calculated as equation (16):

$$A_V = g_{m101} \times Z_{out,LA} \tag{16}$$

In which, the output impedance of each stage can approximately be as equation (17):

$$Z_{out,LA} = \frac{r_{o104}.c_{gs103}.S+1}{g_{m103}+c_{gs103}.S}$$

(17)

On the other hand, cascading three stages of amplifiers results in lowering the bandwidth. In order to analyze this effect, the transfer function of the LA stage is assumed as;  $A_v = \frac{A_{V0}.W_n^2}{S^2 + 2\xi W_n.S + W_n^2}$ , Where,  $\xi$  is the corresponding damping factor, the -3db frequency for each cell gain can be written as equation (18) [18]:

**Fig. 13.** (a) Block diagram of the Limiting Amplifier (b) Structure of each cell gain

Fig. 14. Equivalent circuit of each cell gain of LA stage

$$w_s = \left[1 - 2\xi^2 + \sqrt{(1 - 2\xi^2)^2 + 1}\right]^{\frac{1}{2}} \times w_n \tag{18}$$

Thus, for a three stage amplifier -3db frequency can be written as follows [8]:

$$w_C = \left[1 - 2\xi^2 + \sqrt{(1 - 2\xi^2)^2 - \left(1 - 2^{\frac{1}{2}}\right)}\right]^{\frac{1}{3}} \times w_n \tag{19}$$

In which, to obtain a flat response,  $\xi$  is considered to be equal to  $\sqrt{2}/2$ .

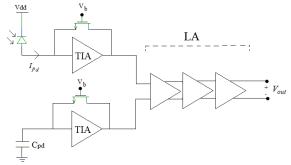

### 6. RECEIVER SYSTEM

Block diagram of the simulated receiver system is shown in figure (15). Two TIA stages are used one for amplifying the main signal plus noise and the other for amplifying the noise. Therefore, the noise of TIA stage can be decreased due to common mode rejection in differential LA stages.

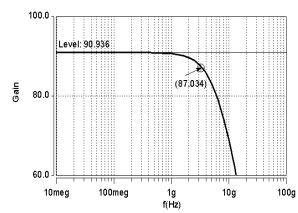

Figure (16) shows the frequency response of the receiver system with the gain of  $90.9 db\Omega$  and bandwidth of 3.5GHz. Also power dissipation for two stages of TIA and three stages of LA is 6.64mw for 1.2v supply voltage.

Finally, table V compares the proposed TIA with other reported ones and table VI reports the proposed

### Majlesi Journal of Electrical Engineering

receiver system. As it can be considered, the proposed TIA has some priorities.

In table V, the figure of merit is defined as equation (20):

$$FOM = \frac{Gain(\Omega) \times Bandwidth(GHz) \times C_{in}(pF)}{Power\ Consumption(mW) \times Input\ referred\ Noise(\frac{pA}{\sqrt{Hz}})}$$

(20)

Fig. 15. Block diagram of the proposed optical receiver

**Fig. 16.** Frequency response of the optical receiver system

**Table 5.** Comparison of the proposed TIA with other works

|                   | Table 3. Com | parison of the pro | pposeu 11A with | other works         |             |

|-------------------|--------------|--------------------|-----------------|---------------------|-------------|

| Ref.              | [4]          | [5]                | [6]             | [11]                | This work   |

|                   |              | [-1                | [-1             | . ,                 |             |

| Tech.             | 65nm         | 0.13µm             | 40nm CMOS       | 0.18µm              | 90nm CMOS   |

|                   | CMOS         | CMOS               |                 | CMOS                |             |

| Supply Voltage    | 1/1.8v       | 1.5v               | 1.3v            | 1.8v                | 1.2v        |

| Power             | 93mw         | 68.6mw             | 103mw/ch        | 18.6mw              | 1.52mw      |

| Consumption       |              |                    |                 |                     |             |

| Gain              | 83dbΩ*       | 600kΩ*             | 64dbΩ           | $55 	ext{db}\Omega$ | 53.9dbΩ     |

| Bandwidth         | 20.5         | -                  | 14.5GHz         | 7GHz                | 3.5GHz      |

| Speed             | 25Gbps       | 5Gbps              | 4×25Gbps        | 10Gbps              | 5Gbps       |

| Input referred    | 1.8µArms     | -                  | 22.4pA/√Hz      | 17.5pA/√Hz          | 15.26pA/√Hz |

| noise             |              |                    |                 |                     |             |

| Input capacitance | 160fF        | 1pF                | 100fF           | 0.2pF               | 160fF       |

| FOM               | _**          | -                  | 1.02            | 2.5                 | 11.73       |

| Year              | 2014         | 2014               | 2014            | 2010                | 2017        |

<sup>\*</sup>whole receiver (TIA+LA)

**Table.6.** Properties of the proposed optical receiver

| •                    | TIA                 | LA     |

|----------------------|---------------------|--------|

|                      | IIA                 | LA     |

| Gain                 | 53.9dBΩ             | 37dB   |

| Bandwidth            | 3.5GHz              | 3.9GHz |

| Power Consumption    | 1.52mW              | 3.6mW  |

| Supply Voltage       | 1.2v                | 1.2v   |

| Input referred noise | $15.26pA/\sqrt{Hz}$ | -      |

| Input capacitance    | 0.16pF              | -      |

| Output capacitance   | -                   | 100fF  |

# 7. CONCLUSION

In this paper, a 5Gb/s low power optical communication receiver system is proposed. A new proposed and structure is discussed mathematically. In order to verify the proper performance and proper output signal of the circuit, required simulations are done. Three stages of differential LAs are added to the TIA and hence lowpower receiver is obtained. The TIA stage shows 53.9dbΩ trans-impedance gain, 3.5GHz bandwidth, 963nA<sub>rms</sub> input referred noise and only 1.52mw power dissipation for 1.2v. The whole receiver system (2 stages of TIA and 3 stages of LA) shows  $90db\Omega$  gain, 3.5GHz bandwidth, 6.64mw power dissipation for 1.2

<sup>\*\*</sup>Gain of the TIA is not specified

supply voltages. Finally, the results indicate that the proposed receiver system is suitable to work as low power 5Gb/s optical communication receiver.

#### REFERENCES

- [1] B. Razavi, "Design of integrated circuits for optical communications", Wiley series in lasers and applications, 2<sup>nd</sup> edition, 2003.

- [2] F. Aznar, S. Celma and B. Calvo, "CMOS Receiver Front-Ends for Giga-bit short-range optical Communications", Springer Science + Business Media New York, 2013.

- [3] C. Li, S. Palermo, "A Low-Power 26GHz Transformer-based Regulated Cascode SiGe BiCMOS Trans-impedance Amplifier", IEEE Journal of Solid-State Circuits, Vol. 48, No. 5, pp. 1264-1275, 2013.

- [4] D. Li, G. Minoia, M. Repossi, D. Baldi, E. Temporiti, A. Mazzanti, F. Svelto "A Low Noise Design Technique for High Speed CMOS Optical Receivers", *IEEE Journal of Solid State Circuits*, 2014, Vol. 49, No. 6, pp. 1437-1446.

- [5] B. Nakhkoon and H. M. Mostafa, "A 5Gb/s Noise Optimized receiver Using a Switched TIA for Wireless Optical Communications", IEEE Transactions on Circuits and Systems, 2014, Vol. 61, No. 4, pp. 1255-1268.

- [6] Y. H. Chien, K. L. Fu, and Sh. Liu, "A 3-25Gb/s Four Channel Receiver with Noise-Cancellation TIA and Power Scalable LA", IEEE Transactions on Circuits and Systems-II, 2014, Vol. 61, No.11, pp. 845-849.

- [7] S. Galal, and B. Razavi, "10Gb/s limiting amplifier and laser/modulator driver in 0.18um CMOS technology", Digest of IEEE ISSCC, pp. 188-189, 2003.

- [8] Ch. Wu, Ch. Lee, W. Chen, and Sh. Liu, "CMOS Wideband amplifier using multiple inductive-series peaking technique", *IEEE journal of solid-state Circuits*, Vol. 40, pp. 548-552, 2005.

- [9] M. Sanduleanu and E. Stikvoort, "Inductor-less 10Gb/s limiter with 10mv sensitivity and offset/temperature compensation in baseline CMOS18", Proc. Of the 29th European Solid-State circuits conference, pp. 153-156, 2003.

- [10] M. Atef and H. Zimmerman, "Low Power 10 Gb/s Inductor-less Inverter based Common-drain Active feedback Trans-impedance Amplifier in 40nm CMOS", Springer Analog Integrated Circuits and Signal processing, 2013, Vol. 76, No. 3, pp. 367-376.

- [11] Zh. Lu, K. Yeo, W. M. Lim, M. A. Do and Ch. Boon, "Design of a CMOS Broadband Transimpedance Amplifier with Active Feedback", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2010, Vol. 18, No. 3. pp. 461-470.

- [12] M. Seifourid, P. Amiri and M. Rakide, "Design of broadband Trans-impedance Amplifier for Optical Communication Systems", Elsevier Microelectronics Journal, 2015, Vol. 46, pp. 679-684.

- [13] B. Razavi, "Design of Analog CMOS Integrated Circuits", MacGraw Hill Series in Electrical and Computer Engineering, 2002.

- [14] S. Galal and B. Razavi, "Broadband ESD protection circuit in CMOS technology" Digest of IEEE ISSCC, pp. 182-183, 2003.

- [15] Ch. Ta Chan, O. T-C Chen, "Inductor-less 10Gb/s CMOS Trans-impedance Amplifier Using Sourcefollower Regulated Cascode and Double Threeorder Active Feedback", IEEE International Symposium on Circuits and Systems, pp. 5487-5489, 2006.

- [16] M. Atef, H. Zimmerman, "Optical Receiver Using Noise Cancelling with an Integrated Photodiode in 40nm CMOS Technology", IEEE Transactions on Circuits and Systems, 2013, Vol. 60, No. 7, pp. 1929-1936.

- [17] M. Atef, H. Zimmermant, "2.5Gbit/s Transimpedance Amplifier using noise cancelling for Optical Receivers", in IEEE International Symposium on circuits and Systems (ISCAS), 2012, pp. 1740-1743.

- [18] W. Chen, Y. Cheng and D. Lin. "A 1.8v 10Gbps Fully Integrated CMOS Optical Receiver Analog Front End", IEEE Journal of Solid State Circuits, Vol. 40, pp.3904-3907, 2007.

- [19] S. Zohoori, M. Dolatshahi, "An Inductorless 10Gbps trans-impedance Amplifier operating at low supply voltage", Iranian conference on Electrical Engineering, IEEE, pp. 145-148, 2017.