# Four-Leg VSI Based DSTATCOM for Compensating Nonlinear and Unbalanced Loads

S. R. Reddy<sup>1\*</sup>, P. V. Prasad<sup>2</sup>, G.N. Srinivas<sup>3</sup>

Department of Electrical Engineering, GNITC, Ibrahimpatnam Hyderabad, India. Email: sadurajender@gmail.com (Corresponding author)

Department of Electrical Engineering, CBIT, Gandipet, Hyderabad, India.

Department of Electrical Engineering, JNTUCH, Hyderabad, India.

Received: January 2018

Revised: June 2018

Accepted: September 2018

## **ABSTRACT:**

This paper presents a study on the four-leg VSI based distribution static compensator (D-STATCOM) for compensation of neutral, source & PCC current harmonic distortion, PCC voltage regulation and compensation of unbalanced in current waveform. This solution could be used for three-phase four-wire nonlinear and unbalanced load medium voltage distribution system. The proposed control algorithm is developed based on synchronous reference frame theory with the PI controller. The obtained reference current signal from control algorithm is compared in hysteresis band current controller for a better switching of the D-STATCOM. The performance of the system with implementing the D-STATCOM is also analyzed and compared. The proposed control method is implemented on 11/0.4kv medium voltage distribution system and provided effective compensation for reactive power and harmonic distortion mitigation. The simulation results are obtained using MATLAB/SIMULINK.

**KEYWORDS:** Distribution Static Compensator (D-STATCOM), Synchronous Reference Frame (SRF) Theory, PI Controller, Voltage Source Inverter (VSI), Hysteresis Current Controller, Harmonic Distortion.

# 1. INTRODUCTION

In last one decade, power electronic devices are widely used in industrial applications for transferring power in more efficient way [1-3]. The excessive use of power electronic equipments, which represent nonlinear loads, in a distribution network has caused many disturbances in the quality of power such as harmonic pollutions and reactive power problems. As a result, poor power factor, weakening efficiency, overheating of motors and transformers, malfunction of sensitive devices, etc. occur [4-5]. Another power quality problem is the use of single- or three-phase unbalanced and nonlinear loads which causes excess current flowing through neutral wire. In addition, other power quality problems cause excess overload on the neutral wire [6]. The unbalanced in source voltage is also occurred due to unbalanced load. The unbalanced source voltage may generate the lower order harmonic component in the power system and also cause a negative sequence current and torque reduction in case of electric machine drive system [7, 8]. These power quality problems are addressed using custom power devices such as distribution static compensators (DSTATCOM), dynamic voltage restorer (DVR) and unified power quality conditioner (UPQC). In which the distribution static compensators are more suitable

for reactive power compensation and harmonic current mitigation in the distribution network compared to other custom power devices [9]. The DSTATCOM operates in two modes such as transformer-based topology and inverter-based topology. In the transformer-based topology, DSTATCOM includes three-leg VSI combined with zig-zag transformer [10] or T-connected transformer [11] or star-delta transformer, etc. In this scheme, the zero sequence component of current is eliminated using transformer and the positive and negative component of current is compensated using three-leg VSIs. In inverter-based topology, DSTATCOM includes three single phases VSI [12], four-leg VSI [13, 14], three-leg VSI with split phase capacitor [15], and three-leg VSI with neutral terminal at the positive or negative of dc bus [16]. From the mentioned methods, most popularly for nonlinear and unbalanced loads current compensation, the three leg VSI with split phase capacitor or the fourleg VSI are used. The split phase capacitor method requires large dc link capacitor voltages because it handles neutral current directly. Another drawback of voltage unbalance across each dc link capacitor is that, it increases stress over semiconductor switches [17, 18]. These problems can be solved by using four-leg VSI. In this paper four-leg VSI based DSTATCOM

topology is used for better neutral and source current compensation as compared to the split phase capacitor method. The performance of four-leg VSI depends on the implemented control strategy. In this paper, SRF Theory with the Proportional Integral (PI) controller technique is used. The tuning of the PI controller is done via the Ziegler-Nichols method. Many authors have proposed and implemented different control algorithms on 400v distribution systems. In practical applications the distribution system is stepped down to 400v using 11/0.4 kv three phase transformer. By connecting DSTATCOM at the PCC harmonic and reactive power is compensated due to linear/nonlinear and balanced/unbalanced loads. In the above proposed method, the effect of transformer (11/0.4kv) is not taken into consideration. In this paper, 11/0.4kv distribution transformer is considered. The harmonic and reactive power compensation before and after transformer is considered and analyzed.

In this paper, SRF theory controlled four-leg VSI DSTATCOM is proposed and implemented on 11/0.4kv distribution system. The performance of the proposed DSTATCOM is analyzed under nonlinear and unbalanced loads conditions in terms of harmonic mitigation, neutral current compensation and voltage regulation at the PCC. The proposed results are validated using MATLAB/SIMULINK software. The paper is organised as follows; section 2 presents system configuration, section 3 represents control strategy, section 4 gives the results & discussion, finally section-5 gives conclusions.

## 2. SYSTEM CONFIGURATION

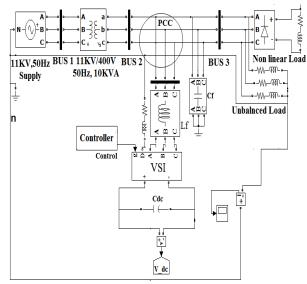

Fig.1 shows the system configuration of proposed Distribution static compensator (D-STATCOM) for the three phase four wire distribution system with nonlinear and unbalanced loads. Three phase source voltage of 11kv is stepped down to 400V by using 11/0.4Kv three phase distribution transformers and connected to nonlinear and unbalanced loads. The connected unbalanced nonlinear load introduces harmonic at the PCC. By Connecting DSTATCOM at the PCC, the unbalanced at the PCC and in load voltage wave form is eliminated and also current harmonics are mitigated. The DSTATCOM consist of four-leg voltage source inverter with interface inductor  $(L_f)$ . Here the dc link capacitor (Cdc) and voltage across the capacitor is Vdc selected as 1.6 times the peak value of the source voltage [19]. The four-leg VSI consists eight IGBT switches. In six IGBTs, switches are used for compensating harmonics and unbalanced in current wave and remaining two IGBTs switches are used for neutral current compensation. The nonlinear load consists of three phase bridge rectifier with R-L load. The fourth leg provides effective neutral current

## Vol. 12, No. 4, December 2018

compensation compared to the split phase capacitor method. The unbalanced load consists of three phase loads having three different magnitudes of resistance and inductance values. The rating of the transformer kept 20kva. Here the capacitor filter (cf) is used for eliminating harmonic in voltage wave form. The main advantage of the proposed model is that the requirements of filters are eliminated.

Fig. 1. The system configuration.

# 3. CONTROL STRATEGY

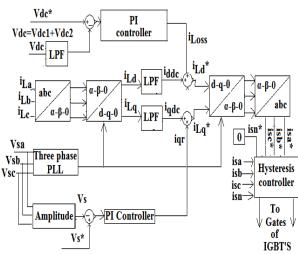

The block diagram of the proposed SRF control algorithm is shown in Fig 2. The control algorithm is used for extracting the fundamental reference control signals to switching of VSI based DSTATCOM for harmonic and reactive power compensation during unbalanced nonlinear load condition.

Fig. 2. The block diagram of the proposed control algorithm.

The nonlinear load currents consist of active, reactive and harmonic current in three phase system. In this, the reactive and harmonic components of currents are separated, for compensation. The separation includes converting the instantaneous three phase load currents into two phase stationary  $\alpha$ - $\beta$ -0 axis using Clark's transformation equation given in eq. (1).

$$\begin{bmatrix} i_{L0} \\ i_{L\alpha} \\ i_{L\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1/\sqrt{2} & 1/\sqrt{2} & 1/\sqrt{2} \\ 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} i_{La} \\ i_{Lb} \\ i_{Lc} \end{bmatrix}$$

(1)

The stationery  $\alpha$ - $\beta$ -0 current axis components are transformed into d-q-0 (d-direct axis, q-quadrature axis components) rotating reference frame by using below park transformation equation.

$$\begin{bmatrix} i_{L0} \\ i_{Ld} \\ i_{Lq} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos\theta & \sin\theta \\ 0 & -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} i_{L0} \\ i_{L\alpha} \\ i_{L\beta} \end{bmatrix}$$

(2)

Here the  $\theta$  is the transformation angle. The  $\cos\theta$  and  $\sin\theta$  is obtained from the three phase PLL block (phase locked loop) of voltage source for synchronization of voltage and current. The obtained  $i_{Ld}$  and  $i_{Lq}$  current components are called instantaneous active and reactive load current components. Each current component has an average value (dc component) and oscillating value (ac component) as given in equation (3) & (4).

$$i_{Ld} = i_{ddc} + i_{dac}$$

(3)

$$i_{Lq} = i_{qdc} + i_{qac} \tag{4}$$

Where,  $i_{d\ dc}$  and  $i_{q\ dc}$  are the average or dc component of  $i_{Ld}$  and,  $i_{d\ ac}$  and  $i_{q\ ac}$  are the oscillating or ac component of  $i_{Lq}$ .

The oscillatory component (harmonic) appears like ripples. After eliminating the oscillatory current component by using Low pass filter, the average active and reactive current components are given in Equation (5) & (6).

$$i_{Ld} = i_{ddc}$$

(5)

$$i_{Lq}=i_{qdc}$$

(6)

In order to maintain the constant DC link voltage and to supply the losses in DSTATCOM, the output current of the PI controller is considered as loss current component,  $(i_{Loss})$  is added to the average active reference current component of d-axis in d-q frame. Then the active reference current component is

$$\mathbf{i}_{\mathrm{Ld}}^{*} = \mathbf{i}_{\mathrm{ddc}} + \mathbf{i}_{\mathrm{loss}} \tag{7}$$

#### Vol. 12, No. 4, December 2018

The loss reference component of current ( $i_{LOSS}$ ) is extracted, by comparing the reference dc bus voltage  $V_{dc^*}$  with the actual dc bus voltage  $V_{dc}(V_{dc}=V_{dc1}+V_{dc2})$  of VSI at the n<sup>th</sup> sampling instant

$$\mathbf{V}_{de(n)} = \mathbf{V}_{dc^*(n)} - \mathbf{V}_{dc(n)} \tag{8}$$

The compared error signal  $V_{de(n)}$  is processed through a PI controller to compute the loss component ( $i_{Loss}$ ) at n<sup>th</sup> sampling instant, as follows below;

$$i_{\text{Loss}(n)} = i_{\text{loss}(n-1)} + k_{\text{pd}} (V_{\text{de}(n)} - V_{\text{de}(n-1)}) + k_{\text{id}} V_{\text{de}(n)}$$

(9)

Here the  $k_{pd}$  and  $k_{id}$  are the proportional and integral gains of PI controller. The output of the PI controller is the loss reference component ( $i_{Loss}$ ) of the DSTSTCOM. The loss reference current component ( $i_{loss}$ ) is added to the average active reference component ( $i_{Ld}$ ) for regulating the active reference component of the current ( $i_{Ld*}$ ).

The direct axis reference current component  $(i_{Ld}^*)$  is used for compensation of harmonic and power factor. Similarly for regulating the voltage at the PCC, the source must need to deliver the reactive current  $(i_{qr})$ , to be added to the average reactive reference component of current  $(i_{q \ dc})$  of q-axis in d-q frame same as direct current axis component. Then the resultant reactive reference current component is

$$\mathbf{i}_{\mathrm{Lq}} = \mathbf{i}_{\mathrm{qdc}} + \mathbf{i}_{\mathrm{qr}} \tag{10}$$

The reactive current  $(i_{qr})$  is obtained from the PI controller output, the input to the PI controller is obtained by subtracting the voltage amplitude Vs from the reference voltage Vs\* and is fed to PI controller. Here the amplitude of the PCC voltage is given as

$$V_{s} = \sqrt{\frac{2}{3} \left( V_{sa}^{2} + V_{sb}^{2} + V_{sc}^{2} \right)}$$

(11)

The PI controller output is given as

$$V_{qr(n)} = V_{qr(n-1)} + K_{pq}(V_{te(n)} - V_{te(n-1)}) + K_{iq}V_{te(n)}$$

(12)

Where  $V_{te(n)}$  =V\*\_s-V\_{s(n)} is the error between the reference (V\*\_s) and actual(V\_s) terminal voltage amplitude at the nth sampling instant. Here  $K_{pq}$  and  $K_{iq}$  are the proportional and the integral gains of the PI controller. The reactive reference current component ( $i_{Lq}$ \*) is used for ac voltage regulation and compensation of load reactive power.

The Active and reactive reference current component ( $i_{Ld}^*$ ,  $i_{Lq}^*$ ) are transformed in to  $\alpha$ - $\beta$ -0 frame obtained by using inverse park's Equation (13).

$$\begin{bmatrix} \mathbf{i}_{S0} \\ \mathbf{i}_{S\alpha} \\ \mathbf{i}_{S\beta} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos\theta & -\sin\theta \\ 0 & \sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} \mathbf{i}_{L0} \\ \mathbf{i}_{Ld} \\ \mathbf{i}_{Lq} \end{bmatrix}$$

(13)

The reference currents from the Inverse Park's are transformed into three phase reference current (a-b-c) by using inverse Clark's Equation (14).

$$\begin{bmatrix} i_{s\alpha} \\ i_{sb} \\ i_{sc} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 0 & 1 & 0 \\ 0 & -1/2 & \sqrt{3}/2 \\ 0 & -1/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} i_{s0} \\ i_{s\alpha} \\ i_{s\beta} \end{bmatrix}$$

(14)

The obtained three phase reference currents  $(i_{sa}^*, i_{sb}^*, i_{sc}^*)$  are compared with the actual compensating filter currents  $(i_{sa}, i_{sb}, i_{sc})$  in hysteresis band controller for better switching of VSI of IGBT's. The main advantage of this hysteresis band controller is that it's easy implementation, better stability, faster response as compared to the other controller like carrier based, bead beat and feed forward etc. [20].

The neutral current compensation is obtained using fourth leg VSI. The gate switching of reaming two IGBTs of fourth leg VSI is obtained by comparing the reference neutral current  $(i_{sn}^*)$  with actual compensating neutral current  $(i_{sn})$  in hysteresis band controller.

$$I_{sn} = -(i_{sa} + i_{sb} + i_{sc})$$

(15)

$$i_{sn} * = 0$$

(16)

#### 4. RESULTS AND DISCUSSION

The proposed four-leg VSI based DSTATCOM model is implemented in MATLAB/SIMULINK software by using synchronous reference frame control algorithm with PI controller. The model is verified under nonlinear and unbalanced load condition. The proposed model is used for unbalanced compensation, harmonic mitigation, power factor correction at the PCC. The simulation period is taken from 0.2s to 0.3s for the better observation. The A, B, C Phase wave forms are indicated by red, green, blue lines. Neutral wave form is indicated by black line. The performance of DSTATCOM is observed for the following cases:

- Nonlinear and unbalanced without DSTATCOM

- DSTATCOM with PI Controller

- Neutral current compensation

- Power factor improvement

- Reactive power compensation

- THD analysis.

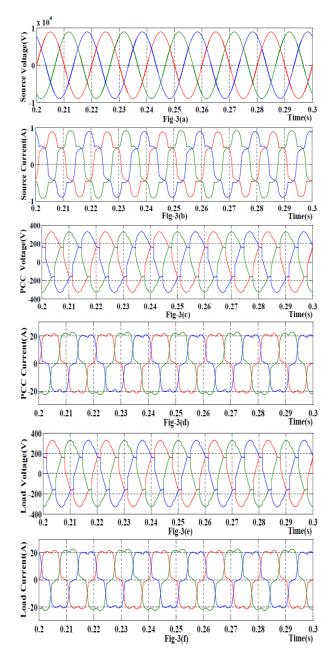

#### 4.1. Nonlinear & Unbalanced without DSTATCOM

When nonlinear & unbalanced load is connected to the proposed distribution system, it causes harmonics

#### Vol. 12, No. 4, December 2018

and unbalanced in source current (Bus-1) as shown in Fig 3(b). The nonlinear & unbalanced load also introduces harmonics at the PCC voltage & current wave form (bus-2).is shown in Figs 3(c) & 3(d). The harmonics current effects the loads connected the PCC. Figs 3(e) & 3(f) shows the load voltage and load current. Fig 3(g) shows the phase current of Phase-A at the PCC.

Fig. 3. (a)Source voltage wave form, (b). Source current wave form, (c). voltage waveform at the PCC (Bus-2), (d). Current waveform at the PCC (Bus-2), (e).Load voltage wave form, (f).Load current wave form, (g). Phase current wave form –A at the PCC, during unbalanced nonlinear load without D-STATCOM.

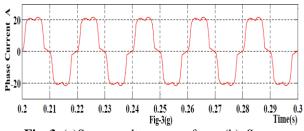

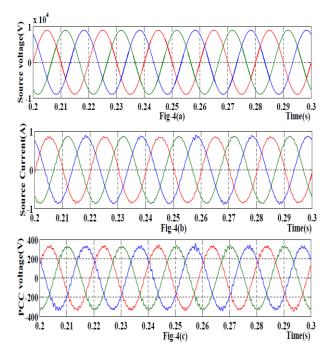

# 4.2. DSTATCOM with PI Controller

When SRF controlled D-STATCOM is connected at the PCC, the D-STATCOM is injecting the required amount of reactive power for compensation of source and PCC current harmonics and unbalanced in the waveform also. The DC-link voltage is regulated by implementing the PI controller. The compensated source current waveforms are shown in Fig 4(b). Figures 4(c) and 4(d) show the compensated voltage and current waveform at the PCC. Load voltage and current waveform is shown in Fig 4(e) and 4(f). Phase current waveform Phase-A at the PCC is shown in Fig4 (g). The DC-link voltage (Vdc=Vdc1+Vdc2) wave form is shown in Fig 4(h). The compensating filter currents are shown in Fig 4(i).

**Fig. 4.** (a)Source voltage wave form, (b). Source current wave form, (c). voltage waveform at the PCC (Bus-2), (d). Current waveform at the PCC (Bus-2), (e). Load voltage wave form, (g). Phase current wave form of phase-A. at the PCC (h). DC-link voltage form (Vdc), (i) compensating filter currents, with PI

controlled D-STATCOM.

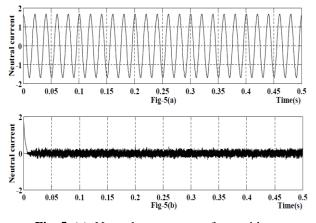

#### 4.3. Neutral Current Compensation

The unbalanced loads cause current flowing through the neutral wire. The current flowing through neutral wire during unbalanced load condition is observed as shown in Fig 5(a). By providing appropriate control algorithm with four leg VSI current in supply neutral wire is compensated and is observed as shown in Fig 5(b), with four-leg VSI, which

provides effective compensation for the both neutral current and line currents of the proposed system.

## 4.4. Power Factor Improvement

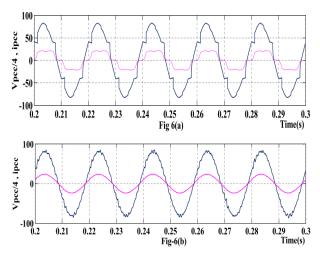

**Fig. 6**. (a). Voltage and current wave form without compensation, (b). Voltage and current wave form after compensation, R-phase.

Figs 6(a) and 6(b) show that voltage and current waveform of R-phase without and with DSTATCOM for observation of improvement in power factor. The power factor improvement with and without DSTATCOM can be observed from the Table-1.

| Table | 1. | Power    | factor | improvement | analysis   |

|-------|----|----------|--------|-------------|------------|

| Labic |    | 1 0 1 01 | inclui | mprovement  | unury 515. |

| Corresponding<br>BUS | Without<br>DSTATCOM | With<br>DSTATCO<br>M |

|----------------------|---------------------|----------------------|

| BUS-1(SOURCE)        | 0.9514              | 0.9971               |

| BUS-2 (PCC)          | 0.9754              | 0.9998               |

| BUS-3 (Load)         | 0.9754              | 0.995                |

#### Vol. 12, No. 4, December 2018

From the Table 1, It is observed that by connecting DSTATCOM at the PCC, power factor is improved at the source side (BUS-1) as well as at the PCC (BUS-2).

#### 4.5. Reactive Power Compensation

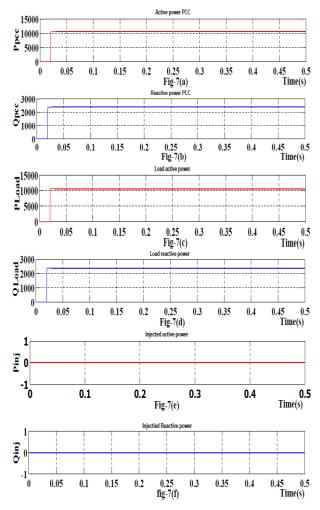

The amount of active and reactive power, are transferred from the source to load without compensating device as shown in Fig 7. The Figs 7(a) and 7(b) show the active and reactive power supplied by source. The required load active and reactive power are shown in the Figs 7(c) and 7(d). The compensating device will not inject any active & reactive power to the load.

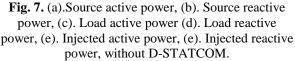

When the DSTATCOM is connected to the proposed system at the PCC. The required amount of reactive power to the load is supplied from the DSTATCOM and the source is not supplying any reactive power which is observed from the Fig 8. The

Figs 8(a) and 8(b) show the active and reactive power supplied by source. The load active and reactive power are shown in Figs 8(c) and 8(d). The injected active and reactive power DSTATCOM at the PCC are shown in Figs 8(e) and 8(f).

Fig. 8. (a) Active power at the PCC Bus, Fig-(b). the reactive power at the PCC Bus. Fig-(c). Active power at the Load Bus, Fig-(d). the reactive power at the Load Bus. Fig-(e). Injected active power, Fig-(f). the Injected reactive power.

## 4.6. Total Harmonic Distortion analysis

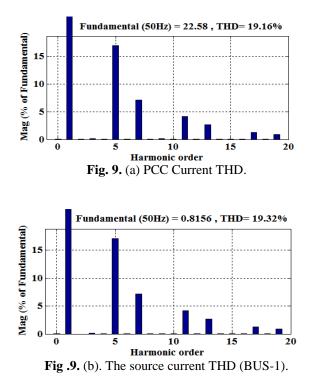

The total harmonic distortion of the PCC and source currents wave forms for the proposed system with and without DSTATCOM is discussed here.

a. Nonlinear & unbalanced load without DSTATCOM

## Vol. 12, No. 4, December 2018

The total harmonic distortion of the system by connecting nonlinear and unbalanced load without DSTATCOM is shown in Fig 9. The Current harmonic distortion at the PCC (BUS-2) is observed 19.16% as shown in Fig 9(a). The source current harmonic distortion is 19.32% as shown in Figure 9(b).

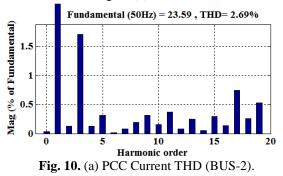

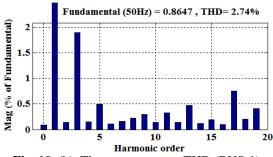

## **b. DSTATCOM with PI Controller**

BY Connecting DSTATCOM to the proposed system, the current harmonics distortion at the PCC (BUS-2) is reduced to 2.43% as shown in Fig 10 (a). The source current harmonic distortion is reduced to 2.02%, as shown in Fig 10 (b).

Fig. 10. (b). The source current THD (BUS-1).

| Table 2. The THD analysis. |                    |       |                    |       |                    |      |  |  |  |

|----------------------------|--------------------|-------|--------------------|-------|--------------------|------|--|--|--|

| Wii                        | isa                | THD   | isb                | THD   | isc                | THD  |  |  |  |

| Without DSTSTCOM           | 0.82               | 19.3  | 0.850              | 18.44 | 0.82               | 19.0 |  |  |  |

|                            | V <sub>pcc a</sub> | THD   | V <sub>pcc b</sub> | THD   | V <sub>pcc c</sub> | THD  |  |  |  |

|                            | 319                | 11.33 | 317.2              | 11.48 | 318.1              | 11.8 |  |  |  |

|                            | Ipcc a             | THD   | Ipcc b             | THD   | Ipcc c             | THD  |  |  |  |

|                            | 22.6               | 19.16 | 23.7               | 18.18 | 21.8               | 19.9 |  |  |  |

|                            | V <sub>La</sub>    | THD   | V <sub>Lb</sub>    | THD   | V <sub>Lc</sub>    | THD  |  |  |  |

|                            | 319                | 11.33 | 317.2              | 11.48 | 318.1              | 11.8 |  |  |  |

| With DSTATCOM              | i <sub>Sa</sub>    | THD   | i <sub>Sb</sub>    | THD   | isc                | THD  |  |  |  |

|                            | 0.87               | 2.74  | 0.85               | 2.38  | 0.85               | 2.27 |  |  |  |

|                            | V <sub>pcc a</sub> | THD   | V <sub>pcc b</sub> | THD   | V <sub>pcc c</sub> | THD  |  |  |  |

|                            | 325                | 4.24  | 325                | 4.00  | 325                | 3.63 |  |  |  |

|                            | I <sub>pcc a</sub> | THD   | Ipcc b             | THD   | Ipcc c             | THD  |  |  |  |

|                            | 23.6               | 2.69  | 23.4               | 2.19  | 23.4               | 2.58 |  |  |  |

|                            | V <sub>La</sub>    | THD   | V <sub>Lb</sub>    | THD   | V <sub>Lc</sub>    | THD  |  |  |  |

|                            | 325                | 4.24. | 325                | 4.00  | 325                | 3.63 |  |  |  |

Total harmonic distortion analysis of without and with DSTATCOM for each phase is observed form the Table 2.

## 5. CONCLUSION

In this paper, the performance of four-leg VSI based DSTATCOM has been analyzed and implemented using synchronous reference frame control algorithm. The four-leg inverter provided better neutral, PCC current compensation compared to other inverter topology performance, and it also reduces the requirements of filters. The dc bus voltage is maintained constant under all disturbance conditions by using PI controller. The control logarithm is simple and provided better compensation for reactive power, harmonic, neutral current, unbalanced in currents and voltage regulation at the PCC in three phase three wire nonlinear and unbalanced load distribution system. The proposed control algorithm on the 11/0.4kv distribution system model is working satisfactory and provided better harmonic compensation at the PCC and source side. The simulation results are obtained using MATLAB/SIMULINK software.

#### Vol. 12, No. 4, December 2018

#### REFERENCES

- [1] J. B. Bose, "Global Energy Scenario and Impact of Power Electronics in 21st. Century," *IEEE Trans. Ind. Electron.*, Vol. 60, No. 7, pp. 2638-2651, July 2013.

- [2] Phipps JK, Nelson JP, Sen PK., "Power Quality and Harmonic Distortion On Distribution Systems," *IEEE Trans Ind Appl*, Vol. 30, pp. 476-84, 1994.

- [3] Hive S, Chatterjee K, Fernandes BG. "VAr Compensation and Elimination Harmonics in Three-Phase Four-Wire System Based on Unified Constant Frequency Integration Control", In: IEEE 11th international conference on harmonics and quality of, power, pp. 647–51, 2004.

- [4] George M, Basu KP. "Modelling and Control of Three-Phase Shunt Active Power filter", Am. J. Appl Sci., Vol. 5(5), pp. 1064–70, 2008.

- [5] Acha E, Agelids V, Anaya-Lara O, Miller T. "Power Electronic Control in Electric Systems", *1st ed. Oxford: Newness Power engineering series*; 2002.

- [6] Manoj Kumar M.V, and. Mishra, Mahesh K, "Three-Leg Inverter Based distribution static compensator Topology for Compensating Unbalanced and Nonlinear Loads", *IET power* electronics., Vol.8, No.11, pp. 2076-2084, 2015.

- [7] Akagi H, Watanabe EH, Aredes M. "Instantaneous Power Theory and Applications to Power Conditioning", New Jersey, USA: John Wiley & Sons; 2007.

- [8] Fuchs EwaldF, Mausoum Mohammad AS. "Power Quality in Power Systems and Electrical Machines", London, UK: Elsevier Academic Press; 2008.

- [9] A. Ghosh and Gerard Ledwich, "Power Quality Enhancement Using Custon Power Devices", *Kluwer Academic Publishers*, USA, 2002 April 1955.

- [10] B. Singh, P. Jayaprakash, T. R. Somayajulu, and D. Kothari, "Reduced Rating Vsc with A Zig-Zag Transformer for Current Compensation in A Three-Phase Four-Wire Distribution System," *IEEE Trans. on Power Del.*, Vol. 24, No. 1, pp. 249–259, Jan. 2009.

- [11] B. Singh, P. Jayaprakash, and D. Kothari, "A T-Connected Transformer and Three-Leg VSC based DSTATCOM for Power Quality Improvement," *IEEE Trans. on Power Electron.*, Vol. 23, No. 6, pp. 2710–2718, 2008.

- [12] B. Singh, P. Jayaprakash, D. Kothari, A. Chandra, and K. Al Haddad, "Comprehensive Study of DSTATCOM Configurations," *IEEE Trans. On Ind. Informatics*, Vol. 10, No. 2, pp. 854–870, 2014.

- [13] B. Singh, S. Arya, C. Jain, and S. Goel, "Implementation of Four-Leg Distribution Static Compensator," *IET Generation Transmission Distribution*, Vol. 8, No. 6, pp. 1127–1139, 2014.

- [14] Mahesh K. Mishra, A. Ghosh, A. Joshi, and H. Suryawanshi, "A Novel Method of Load Compensation Under Unbalanced and Distorted Voltages," *IEEE Trans. on Power Del.*, Vol. 22,

No. 1, pp. 288–295, Jan. 2007.

- [15] S. Karanki, N. Geddada, Mahesh K. Mishra, and B. Kumar, "A DSTATCOM Topology with Reduced Dc-Link Voltage Rating for Load Compensation with Nonstiff Source," *IEEE Trans. on Power Electron.*, Vol. 27, No. 3, pp. 1201–1211, Mar. 2012.

- [16] A. Bhattacharya, C. Chakraborty, and S. Bhattacharya, "Parallel Connected Shunt Hybrid Active Power Filters Operating at Different Switching Frequencies for Improved Performance," *IEEE Trans. on Ind. Electron.*, Vol. 59, No. 11, pp. 4007–4019, Nov. 2012.

- [17] S. Srikanthan and Mahesh K. Mishra, "DC Capacitor Voltage Equalization in Neutral Clamped Inverters for DSTATCOM

Vol. 12, No. 4, December 2018

Application," *IEEE Trans. on Ind. Electron.*, Vol. 57, No. 8, pp. 2768–2775, Aug. 2010.

- [18] Y. Chen, B. Mwinyiwiwa, Z. Wolanski, and B.-T. Ooi, "Regulating and Equalizing Dc Capacitance Voltages in Multilevel STATCOM," *IEEE Tran.* On Power Del., Vol. 12, No. 2, pp. 901–907, 1997.

- [19] U. Rao, Mahesh K. Mishra, and A. Ghosh, "Control Strategies for Load Compensation Using Instantaneous Symmetrical Component Theory Under Different Supply Voltages," *IEEE Trans. on Power Del.*, Vol. 23, No. 4, pp. 2310–2317, 2008.

- [20] D. M. Brod and D. Novotny, "Current Control of VSI-PWM Inverters," *IEEE Trans. on Ind. Appl.*, Vol. IA-21, No. 3, pp. 562–570, May 1985.