### Majlesi Journal of Electrical Engineering (MJEE)

https://doi.org/10.57647/j.mjee.2025.17405

# Direct-written AgNP electrodes in all-solution-processed low-voltage organic thin film transistors employing high-k PVP dielectric

Nur Syahadah Yusof<sup>1</sup>, Mohamed Fauzi Packeer Mohamed<sup>1,\*</sup>, Muammar Mohamad Isa<sup>2,3</sup>, Norhawati Ahmad<sup>2,3</sup>, Khatijah Aisha Yaacob<sup>4</sup>, Mohd Hendra Hairi<sup>5</sup>

#### **Original Research**

Received: 20 March 2025 Revised: 6 June 2025 Accepted: 21 June 2025 Published online: 30 August 2025 Published in issue: 25 September 2025

© 2025 The Author(s). Published by the OICC Press under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is prop-

#### Abstract:

Researchers have explored various fabrication methods for organic devices to meet the growing demand for printed electronics and wearables. Inkjet printing has been widely used for deposition of solution-processable materials at low temperatures, making it ideal for flexible electronics. However, nozzle clogging and strict ink and substrate requirements limit its commercialization for OTFTs. Besides, the practical applications of OTFT devices are limited by their high operating voltages. To address these limitations, this study proposes a simple, solution-based fabrication method for developing low-voltage OTFTs on Silicon substrates. A novel direct-write printing technique was utilized to deposit the source/drain electrodes at temperatures below 150 °C in ambient conditions without experiencing nozzle clogging issues, while a spin-coating method was employed for the deposition of TIPS-pentacene semiconducting and high-k PVP dielectric layers. Remarkably, the fabricated OTFT achieved a channel length of 120  $\mu$ m with saturation mobility of 4.49 × 10<sup>-1</sup> cm<sup>2</sup>/Vs, a threshold voltage of -1.5 V, an On/Off current ratio of  $10^8$ , and a subthreshold swing of 66.8 mV/decade, operating below -5 V. The integration of direct-write printing with a high-k dielectric layer offers a new approach for fabricating OTFTs and other organic devices at lower temperatures, making it suitable for flexible electronics.

**Keywords:** Organic thin film transistor; Direct-write printing technique; 6,13-bis(triisopropylsilylethynyl) pentacene; Polyvinylpyrrolidone; Low-voltage; Flexible; Semiconductor devices

#### 1. Introduction

Recently, organic electronics have gained significant attention from researchers, driven by the expansion of the printed electronics industry over the past few decades. Organic electronics represent a promising solution for the development of flexible, low-cost, and large-area electronic applications, including Organic Thin Film Transistors (OTFTs). The OTFT typically comprises three main functional layers, in-

cluding the organic semiconductor (OSC), the dielectric, and the electrodes (i.e., source, drain, and gate terminals) deposited on either a rigid or flexible substrate. The selection of materials and their compatibility with fabrication processes and conditions determined the performance of the device, as highlighted by Yusof et al. in [1]. Therefore, careful consideration of material selection is essential during the device fabrication process.

<sup>&</sup>lt;sup>1</sup>School of Electrical and Electronic Engineering, Engineering Campus, Universiti Sains Malaysia, 14300 Nibong Tebal, Pulau Pinang, Malaysia.

<sup>&</sup>lt;sup>2</sup> Faculty of Electronic Engineering & Technology, Universiti Malaysia Perlis, 02600 Arau, Perlis, Malaysia.

<sup>&</sup>lt;sup>3</sup>Centre of Excellence for Micro System Technology (MiCTEC), Universiti Malaysia Perlis, Arau, 02600, Perlis, Malaysia. <sup>4</sup>School of Material and Mineral Resources Engineering, Engineering Campus, Universiti Sains Malaysia, 14300 Nibong Tebal, Pulau Pinang, Malaysia.

<sup>&</sup>lt;sup>5</sup> Faculty of Electrical Technology and Engineering, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, 76100 Durian Tunggal, Melaka, Malaysia.

<sup>\*</sup>Corresponding author: fauzi.packeer@usm.my

In OTFT devices, the OSC layer plays an essential role as it serves as a channel for charge transport. Pentacene-based OTFTs have drawn substantial attention from researchers due to their high charge mobility [2, 3]. To promote effective charge injection and transport within the device, it is essential that the contacts are compatible with the OSC layer. Theoretically, an Ohmic contact is ideal for the proper operation of OTFTs. Nonetheless, a mismatch between the energy level of the semiconductor and the work function of the electrodes is inevitable, resulting in contact resistance at the metal/semiconductor interface, which is unfavorable for charge transport [4]. Thus, an appropriate electrode material selection is pivotal to optimize the overall OTFT performance.

Continuous efforts have been made to improve the performance of OTFT devices. However, the high operating voltages reaching up to -60 V, particularly in Silicon Dioxide (SiO<sub>2</sub>) based OTFTs, remain a primary concern among researchers. The application of high voltages can exert stress on materials, particularly in flexible substrates, potentially leading to degradation and reducing the lifespan of the device. A low operating voltage in OTFT can be achieved by increasing the gate capacitance. The gate capacitance refers to the capacitance with the gate terminal of the OTFT and can be expressed as (1) [5].

$$C = \varepsilon_0 \varepsilon_r \frac{A}{d} \tag{1}$$

where C is the gate capacitance,  $\varepsilon_0$  is the vacuum permittivity (8.86 × 10<sup>-12</sup> C<sup>2</sup>/Nm<sup>2</sup>),  $\varepsilon_r$  is dielectric permittivity (also known as dielectric constant, k), A is the plate overlap area, and d is the distance between the two plates (also referred to as the dielectric thickness). From (1), the gate capacitance Ccan be increased using materials with a high dielectric constant or reducing the dielectric thickness d [6, 7]. Scaling down the dielectric thickness is not a feasible approach, as it increases leakage currents. Therefore, employing dielectric with a high dielectric constant is a more viable strategy for enhancing the device's gate capacitance in order to reduce its operating voltage.

OTFTs can be developed using various fabrication techniques, contact methods (e.g. screen printing and lithography) or non-contact methods (e.g. inkjet printing). Among these, non-contact inkjet printing has emerged as the most promising technology due to its benefits, including the elimination of the need for a vacuum environment during fabrication, minimized material waste through drop-on-demand technology, and its scalability for large-area manufacturing, as mentioned in [8, 9]. Moreover, its contactless and direct patterning of functional layers prevents morphological damage to the other layers, which is commonly induced by developing and etching processes [10].

Despite its advantages, inkjet printing technology presents several challenges that impede the commercialization of OTFTs, including persistent nozzle clogging issues and stringent requirements for conductive inks (i.e. low viscosity typically between 1 - 25 mPa.s) and substrate properties (i.e. low surface tension between 20 - 50 mN/m) [9, 11]. To address these challenges, a novel fabrication technique employing a direct ink writing (DIW) method has been

proposed to develop OTFTs [12]. Unlike inkjet printing, this method allows the deposition of a wide range of materials, which are not limited to the low-viscosity materials as required in inkjet printing technology. This technique enables layer-by-layer patterning directly from computeraided design (CAD) files and presents a novel bottom-up manufacturing approach for fabricating electronic devices. In this work, we successfully reported all-solutionprocessed low-voltage OTFTs utilizing Silver Nanoparticle (AgNP) conductive ink, Polyvinylpyrrolidone (PVP), and 6,13-bis(triisopropylsilylethynyl) pentacene (TIPSpentacene) as the source/drain electrodes, gate dielectric, and OSC layers, respectively, on a Silicon wafer. Notably, the electrodes were deposited using the proposed DIW printing technique with a channel length of 120 µm. The employment of a high-k dielectric material allows the device to operate at a lower operating voltage of less than -5 V. The rest of this paper is organized as follows: Section 2 outlines the materials utilized and the experimental details involved in the fabrication of the proposed device. This section also presents the electrical and morphological characterizations of the fabricated OTFTs. Subsequently, section 3 analyzes the performance of the devices. These results have been discussed comprehensively and compared with relevant prior work. Finally, section 4 concludes the paper.

#### 2. Method

#### 2.1 Materials

In this study, commercially available Silver Nanoparticle (AgNP) conductive ink from Voltera Inc. was utilized to deposit the conductive electrodes, i.e. source and drain, while 99 + % hydrolyzed Polyvinylpyrrolidone (PVP) (molecular weight = 40,000) purchased from Sigma-Aldrich was employed as the dielectric layer. For the organic semiconducting (OSC) layer, high purity (> 99.9%) 6,13bis(triisopropylsilylethynyl) pentacene (TIPS-pentacene) and its solvent, 99.5% AR-grade Toluene, were obtained from Ossila Ltd. and Chemiz (M) Sdn. Bhd., respectively. All materials were used as received without further purification. A single-side polished < 100 > Silicon substrate, with a thickness of  $625 \pm 25 \,\mu m$  and a resistivity of 1 to 3 mΩ.cm, obtained from Fuleda Technology, was utilized as the substrate for OTFT fabrication.

#### 2.2 Experimental details

This work is organized into two primary sections: Device fabrication using the proposed DIW technique, followed by the electrical and morphological characterization of the fabricated device. Both fabrication and measurements were performed in ambient air at room temperature. Notably, all materials used in this study were solution-processable and applied to the fabrication of Bottom-Gate Bottom-Contact (BGBC) OTFTs.

#### 2.2.1 Fabrication of all-solution-processed low-voltage **OTFT**

Initially, the Silicon (Si) substrate was cut into a 20 mm × 15 mm piece and cleaned using a standard solvent cleaning procedure. The process involved sequential ultrasonic

cleaning in Acetone, Isopropyl Alcohol (IPA), and Deionized (D/I) water for three minutes each. The cleaned substrate was subsequently dried using a dryer before being exposed to ultraviolet (UV) light in the UV/ozone cleaner to remove any residual organic contaminations on its surface. Afterwards, 100 µL of high-k PVP dielectric solution was spin-coated on the cleaned substrate and subjected to heat treatment at 80 °C to 100 °C for one hour.

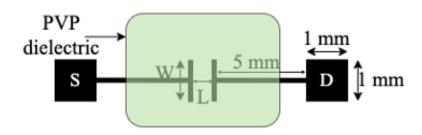

This research utilized a direct-write printing technique for the deposition of source and drain electrodes in OTFT devices. The printer parameters were optimized as described in [12, 13]. To fabricate a bottom-contact device, the source and drain electrodes were DIW printed onto the PVA dielectric layer and subsequently cured at temperatures between 100 °C to 150 °C for one hour. Following this, to complete the OTFT structure, 60 µL of OSC solution was spin-coated onto the source and drain electrodes and annealed at temperatures ranging from 80 °C to 100 °C for 10 minutes to remove any residual solvent. In this work, the OSC solution was prepared by dissolving TIPS-pentacene in Toluene. Finally, any excess OSC material on the surface of the sample was removed using a cotton swab wetted with Toluene. Fig. 1 illustrates the layout of the fabricated device using PVP dielectric on the Si substrate.

#### 2.2.2 Characterization of the fabricated OTFT devices

The fabricated OTFT devices were characterized and analyzed using a Keithley 4200A SCS semiconductor parameter analyzer (SPA) and a quick test system consisting of a custom probe station and optical microscope. The output characteristics were measured by sweeping V<sub>D</sub> from 0 to -5 V, across a range of  $V_G$  from 0 to -5 V. From the output and its corresponding square-root ID curves, the saturation mobility ( $\mu_{sat}$ ), threshold voltage ( $V_{th}$ ), and On/Off current ratio (I<sub>ON</sub>/I<sub>OFF</sub>) were extracted. Furthermore, the subthreshold swing (S) can be calculated from the inverse of the subthreshold slope of the square-root I<sub>D</sub> curve. The morphological characteristics of the deposited TIPS-pentacene film on the PVP/Si substrate were analyzed using scanning electron microscopy (SEM) and atomic force microscopy (AFM), while the surface energy of the PVP dielectric was characterized through contact angle measurements.

#### 3. Results and discussion

## 3.1 Morphological characterization of the proposed

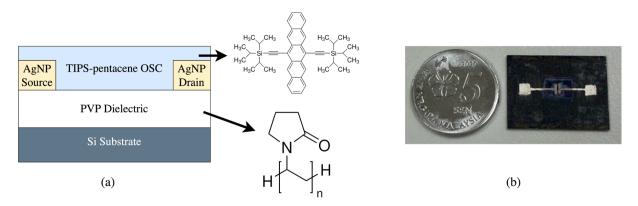

Fig. 2 (a) presents a schematic diagram of the proposed OTFT device, illustrating the materials used in each layer, while Fig. 2 (b) displays the camera photograph of the DIWprinted OTFT device. The OTFT was fabricated on a Si substrate, utilizing AgNP conductive ink for the source and drain electrodes, TIPS-pentacene solution for the OSC layer, and PVP solution for the dielectric layer. This work selected TIPS-pentacene as the OSC layer due to several key advantages that align well with the objectives of OTFT development. One of the primary reasons is its inherently high charge carrier mobility, which is essential for efficient charge transport within the transistor channel, thereby enhancing the overall device performance. TIPS-pentacene also demonstrates excellent crystallinity, a crucial factor that directly influences the mobility of charge carriers by reducing grain boundary scattering and facilitating smoother charge flow.

Another significant reason for selecting TIPS-pentacene is its compatibility with solution-based deposition techniques, such as spin coating, inkjet printing, and drop casting. This compatibility is particularly valuable for scalable and costeffective fabrication processes, as solution processing enables large-area device fabrication and roll-to-roll manufacturing, making it a promising material for commercial applications. Furthermore, TIPS-pentacene exhibits good chemical and structural compatibility with various organic materials commonly used in OTFT fabrication, such as dielectric layers, gate materials, and encapsulation layers. This favorable interaction facilitates the integration of multiple functional layers within the OTFT structure, allowing the development of complex configurations like top-gate and bottom-gate architectures, dual-gate designs, and flexible electronics. The ability to form stable and well-defined interfaces with other organic layers further contributes to the overall stability, reproducibility, and performance of the fabricated OTFTs.

Additionally, the solubility of TIPS-pentacene in common organic solvents provides further flexibility in device processing, enabling fine-tuning of the film morphology, thickness, and uniformity through process parameter adjustments.

Figure 1. Layout of the proposed OTFT device using PVP dielectric on the Si substrate.

Figure 2. (a) Schematic diagram of the device structure and its corresponding chemical structure for OSC and dielectric layers and (b) Camera photograph of the DIW-printed OTFT device on Si substrate.

This adaptability is essential in optimizing the device characteristics to meet specific application requirements, such as in display technologies, sensors, and wearable electronics. Overall, the selection of TIPS-pentacene is justified by its superior electrical properties, processability, and compatibility with OTFT fabrication requirements, making it a highly suitable choice for achieving high-performance organic transistors in this work.

PVP was selected as the dielectric layer in this work due to several critical attributes that align with the performance and fabrication requirements of Organic Thin-Film Transistors (OTFTs). One of the primary reasons is its high dielectric constant (high-k), which is essential for efficiently storing and modulating charges within the transistor. A high-k dielectric allows for greater charge accumulation at the semiconductor-dielectric interface under lower operating voltages, thereby enhancing the overall performance of the OTFT, particularly in low-power applications. In addition to its dielectric properties, PVP is highly compatible with solution-based fabrication techniques such as spin coating, dip coating, and inkjet printing. This compatibility facilitates cost-effective and scalable manufacturing processes, making it suitable for large-area electronic device fabrication. The ability to process PVP from solution also allows for fine control over film thickness and uniformity, which are crucial parameters for achieving consistent and reproducible device performance.

Most importantly, PVP exhibits notable mechanical flexibility, a critical requirement for the development of flexible and wearable electronic devices. Its inherent flexibility enables the fabrication of OTFTs on bendable substrates such as plastic films, allowing devices to withstand mechanical deformation without compromising electrical performance. This property is particularly advantageous in applications like flexible displays, wearable sensors, and foldable electronics, where mechanical durability is as important as electrical functionality.

Furthermore, PVP offers good thermal and environmental stability, which contributes to the long-term reliability of OTFTs, especially in applications subjected to varying environmental conditions. Its ability to form smooth, uniform thin films with low surface roughness also ensures minimal charge trapping at the dielectric-semiconductor interface, thereby enhancing charge carrier mobility and reducing hysteresis in the transistor operation. Overall, the selection of PVP as the dielectric material is justified by its high-k properties for efficient charge modulation, solution processability for scalable fabrication, and excellent mechanical flexibility essential for the next generation of flexible and wearable electronic devices.

Previously, the DIW printing method has been investigated for the development of various sensors and electronic circuits, as reported by Hou et. al. in [14]. Despite its potential applications in printed electronics, the DIW printing technique has not yet been extensively explored for OTFT fabrication. This work successfully employed the DIW printing method to deposit the source and drain contacts in OTFT devices with channel lengths of 120 µm.

The proposed DIW printing technology offers advantages over conventional inkjet printing, particularly in terms of material selection due to its compatibility with a wide range of inks. The AgNP conductive ink used in this work exhibits a high viscosity of 2000 mPa.s. No clogging issues were encountered during the deposition process and the printed electrodes were deposited smoothly onto the substrate, as seen in Fig. 2 (b). The compatibility of the DIW printer with high-viscosity inks exceeds that of inkjet printing technology, which typically accommodates inks with viscosities of up to 25 mPa.s [11]. This capability not only enables the utilization of a broader range of materials but also simplifies the ink formulation process, which is often limited by viscosity to prevent nozzle clogging issues. AgNP conductive ink was used in this work due to its narrow energy barrier with TIPS-pentacene, characterized by an energy gap of less than 0.4 eV, which facilitates efficient hole injection between the electrodes and the OSC layer [15]. Additionally, AgNP ink requires a curing temperature of less than 150 °C, making it well-suited for flexible electronics applications. Maintaining consistent line width during DIW printing is essential to ensure uniformity in printed patterns, which significantly influences the electrical performance and reliability of OTFTs. Variations in line width can result in inconsistencies in channel dimensions, thereby affecting charge transport and overall device performance. A key challenge in achieving uniform line width is the precise control of ink flow rate, which is governed by parameters

such as kick and rheological setpoint. In DIW printing, kick refers to the initial pressure pulse applied to initiate ink flow through the nozzle at the onset of the printing process. Optimizing the kick is crucial to prevent delays in ink extrusion or excessive deposition, both of which can result in line width variations. Similarly, the rheological setpoint defines the ink's flow characteristics, including viscosity and shear-thinning behavior, ensuring an optimal balance between fluidity during extrusion and structural integrity post-deposition. Precise control of both parameters is essential for maintaining consistent line widths, thereby ensuring the uniformity and reliability of printed OTFTs.

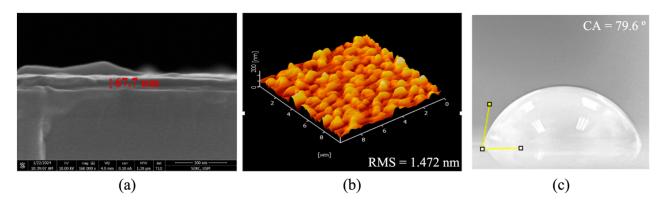

Next, the morphological characteristics of the deposited OSC layer of the fabricated device were analyzed to evaluate the quality of the film, assess its surface roughness, identify any defects or irregularities, and elucidate their relationships to the electrical performance of the device. Fig. 3 presents the morphological characteristics of the fabricated TIPS-pentacene OTFT based on the PVP dielectric layer on the Si substrate. The spin-coated TIPS-pentacene film demonstrated a relatively smooth surface, characterized by surface roughness (RMS) of 1.472 nm (Fig. 3 (b)) and a thickness of 67.7 nm (Fig. 3 (a)).

Surface roughness directly affects the interface quality between the OSC and the dielectric layer, which in turn influences charge carrier mobility, threshold voltage, and overall device stability. A smoother OSC surface reduces the number of trap sites and defects at the interface, thereby minimizing charge scattering and recombination. This leads to higher charge carrier mobility, as the carriers can move more freely through the well-ordered crystalline domains of the TIPS-pentacene film without encountering barriers or interruptions caused by surface irregularities. In contrast, a higher surface roughness would introduce more grain boundaries, voids, and defects, increasing the probability of charge trapping and reducing the effective mobility of carriers within the channel. Furthermore, surface irregularities can result in non-uniform electric fields at the semiconductor-dielectric interface, causing instability in the transistor's threshold voltage and increasing hysteresis during device operation.

The relatively smooth surface observed in this work is attributed to the hydrophobic properties of the PVP dielectric layer, with a contact angle of 79.6° as shown in Fig. 3 (c).

The hydrophobic nature of PVP promotes better molecular ordering of the TIPS-pentacene during the spin coating process, leading to a more uniform and defect-free film. This enhanced film morphology contributes significantly to the stable and high-performance electrical characteristics of the fabricated OTFTs, such as high charge carrier mobility, low threshold voltage, and reduced hysteresis. In summary, the surface roughness of the TIPS-pentacene film is a crucial morphological parameter that correlates directly with the electrical performance of the OTFT. The smooth surface achieved in this study ensures reduced charge trapping, improved charge transport, and stable transistor operation, highlighting the importance of optimizing surface morphology during the fabrication process.

#### 3.2 Electrical characterization of the proposed OTFT

In this section, the electrical characteristics of the proposed OTFT devices were evaluated. Fig. 4 (a) shows the output characteristics ( $I_D - V_D$ ), while Fig. 4 (b) and Fig. 4 (c) depict the transfer characteristics ( $I_D - V_G$ ) of the device and the corresponding square-root  $I_D$  ( $\sqrt{I_D} - V_G$ ) curve, respectively.  $V_D$  was swept from 0 to -5 V with a step size of -1 V, while  $V_G$  was varied from 0 to -5 V. These findings represent the average values obtained from testing across ten devices. Negative voltages were applied because holes serve as the majority charge carriers in TIP-pentacene. From Fig. 4, the proposed TIPS-pentacene OTFT device demonstrates a typical p-type field effect transistor behaviour, with distinct linear and saturation regions observable in the output curves, as shown in Fig. 4 (a).

From the transfer curve and the corresponding square-root  $I_D$  curve displayed in Fig. 4 (b) and Fig. 4 (c), saturation mobility ( $\mu_{sat}$ ) of  $4.49 \times 10^{-1}$  cm<sup>2</sup>/Vs, a threshold voltage ( $V_{th}$ ) of -1.5 V, and On/Off current ratio ( $I_{ON}/I_{OFF}$ ) of up to  $10^8$  (at  $V_G = -5$  V and  $V_D = -2.5$  V) were determined. Additionally, the device achieved the subthreshold swing (S) of 66.8 mV/decade. The field effect mobility of the OTFT in the saturation region was calculated using (S), as described in [19]. On the other hand, the subthreshold swing was determined from the inverse of the subthreshold slope of the square-root  $I_D$  curve and can be expressed as (3), as outlined in [20]. Apart from that, the subthreshold swing can also be represented by (4), which can be employed to

Figure 3. Morphological characterization of the fabricated device: (a) SEM cross-sectional image and (b) AFM surface profile of the TIPS-pentacene layer, and (c) water contact angle of PVP dielectric layer.

$\textbf{Figure 4.} \ \ \text{Electrical characterization of the fabricated device:} \ \ (a) \ \ \text{Output} \ \ (I_D-V_D), \ \ (b) \ \ \text{Transfer} \ \ (I_D-V_G), \ \text{and} \ \ (c) \ \ \text{Square-root} \ \ I_D \ \ (\sqrt{I_D}-V_G) \ \ \text{curves.}$

calculate the lowest theoretical S at room temperature.

$$\mu_{\text{sat}} = \frac{L}{W} \frac{1}{C_i} \frac{\delta^2 I_D}{\delta V_G^2}$$

(2)

where  $\mu_{\text{sat}}$  is the saturation mobility,  $C_i$  is the capacitance of the dielectric, while L and W are the channel length and width, respectively.

$$S = \frac{dV_{G}}{d(\log I_{D})} \tag{3}$$

$$S = \frac{K_B T}{q} \ln 10 \tag{4}$$

where  $K_B$  is Boltzmann's constant, T is temperature in Kelvin, and q is the elementary charge. At a room temperature of 300 K, the value of S was determined to be 57 mV/decade.

In general, the electrical performance of OTFT devices is closely linked to their morphological characteristics [21]. The quality of OSC film typically influences the mobility

of the device, while the quality of its interface significantly affects the overall performance of the OTFT, including parameters such as  $I_{ON}/I_{OFF}$  and S [22, 23]. The smooth and good adhesion between the deposited TIPS-pentacene and dielectric layers, characterized by low surface roughness (RMS) and subthreshold swing S nearly reaching the theoretical limit at room temperature, improved the overall device performance, exceeding the values reported by other researchers, as indicated in Table 1. Minimal surface defects and interface traps between OSC and dielectric layers facilitate an enhancement of the I<sub>ON</sub>/I<sub>OFF</sub> current ratio by diminishing the leakage currents within the device. As a result, the proposed OTFT significantly enhances its I<sub>ON</sub>/I<sub>OFF</sub> performance, with an improvement of up to eight orders. A subthreshold slope close to the theoretical limit ( $\sim 60 \text{ mV/decade}$  at room temperature) is significant as it indicates efficient gate control over the channel, enabling rapid switching between the off and on states with minimal voltage change. This leads to lower power consumption, reduced leakage current, and faster switching speeds, which

Table 1. Comparison of the proposed all-solution-processed low-voltage OTFT performance with other state-of-the-art works.

| Reference                                                 | [3]                  | [16]                 | [17]                 | [18]                | [12]               | This work            |

|-----------------------------------------------------------|----------------------|----------------------|----------------------|---------------------|--------------------|----------------------|

| S/D Deposition                                            | Lithography          | Inkjet-printed       | Inkjet-printed       | Thermal evaporation | DIW-printed        | DIW-printed          |

| OSC layer                                                 | TIPS-pentacene       | TIPS-pentacene       | TIPS-pentacene       | TIPS-pentacene      | TIPS-pentacene     | TIPS-pentacene       |

| Dielectric layer                                          | SiO <sub>2</sub>     | PVP                  | PVP                  | PVA                 | SiO <sub>2</sub>   | PVP                  |

| Saturation Mobility $\mu_{sat}$ (cm <sup>2</sup> /Vs)     | $3.9 \times 10^{-3}$ | $5.8 \times 10^{-3}$ | $3.0 \times 10^{-2}$ | $3.4\times10^{-2}$  | $4.3\times10^{-5}$ | $4.5 \times 10^{-1}$ |

| Operating voltage (V)                                     | 0 to -20             | 0 to -12             | 0 to -3              | 0 to -30            | 0 to -60           | 0 to -5              |

| Threshold Voltage $V_{th}$ (V)                            | -4.7                 | -5.8                 | -0.7                 | -13.8               | -0.4               | -1.5                 |

| On/Off Current<br>Ratio I <sub>ON</sub> /I <sub>OFF</sub> | -                    | 10 <sup>5</sup>      | $10^{2}$             | 10 <sup>3</sup>     | $10^{2}$           | $10^{8}$             |

| Subthreshold Swing S (mV/decade)                          | -                    | -                    | -                    | 4200                | 100                | 66.8                 |

are critical for energy-efficient, high-performance OTFTs, particularly in flexible and wearable electronics. Achieving a near-ideal subthreshold slope also reflects high interface quality with minimal trap states, enhancing device reliability and scalability, and is often a result of optimized material selection, surface treatment, and fabrication processes.

Apart from that, the fabricated OTFT device displayed improvement in mobility of up to five orders of magnitude as compared to the previously proposed device [12]. The low surface energy of the high-k dielectric layer, characterized by a contact angle of nearly 90°, promotes the growth of the OSC layer by providing a stable foundation for the deposition of the TIPS-pentacene film. This condition enables the formation of a uniform and smooth OSC layer, thereby enhancing its electrical performance, particularly in terms of mobility.

Conventionally, OTFTs have been developed using oxidebased dielectric materials, such as SiO2. Although SiO2 is widely recognized for its excellent insulating properties and compatibility with Si substrates, OTFTs fabricated using this dielectric material often face challenges related to high operational voltages, typically more than -60 V[12, 24, 25]. The high operating voltages in SiO<sub>2</sub>-based OTFTs can be attributed to the intrinsic properties of SiO<sub>2</sub>, including its low capacitance per unit area. While reducing the thickness of SiO<sub>2</sub> can enhance its capacitance density, this approach may lead to higher leakage current in the devices, thereby complicating their operation [26].

To cater for this problem, high-k dielectric materials were employed in OTFT development. In this work, PVP has been utilized as the dielectric layer, thanks to its compatibility with solution processable methods and OSC material, as well as its high dielectric constant (k = 7.7). The operating voltage of the proposed device demonstrated remarkable improvement, enabling operation at voltages below -5 V. The incorporation of high-k dielectrics increases the gate capacitance of OTFTs, facilitating greater charge storage per unit area within the gate dielectric [27]. This improvement enables enhanced electrostatic modulation of the semiconductor channel. Consequently, lower gate voltages are needed to achieve the desired changes in channel conductivity, resulting in lower operational voltages in OTFT devices. Low operating voltages are crucial in flexible electronics since flexible substrates are susceptible to damage and degradation when subjected to high voltages, potentially compromising both the overall performance and lifespan of the devices.

Overall, the performance of the fabricated OTFTs surpassed that of devices manufactured using inkjet printing techniques [16, 17], as presented in Table 1. Based on Table 1, the proposed OTFT device not only exhibited a low operating voltage and low Vth but also demonstrated an enhancement of up to eight orders of magnitude in the I<sub>ON</sub>/I<sub>OFF</sub> current ratio. This device also displayed the highest  $\mu_{sat}$ , exceeding that of devices fabricated using thermal evaporation [18]. In summary, the results presented in Table 1 confirm that the proposed DIW printing technique can be effectively utilized to develop OTFT devices without compromising their electrical and morphological performances. Besides, the utilization of high-k dielectric successfully reduced the operating voltage of the proposed device. Notably, this technique allows the deposition of the source and drain electrodes with micrometre channel lengths without encountering clogging issues. The integration of DIW printing technology into the high-k dielectrics offers a novel bottom-up approach for fabricating organic devices, particularly OTFTs, at lower processing temperatures suitable for flexible and wearable electronics niches.

#### 4. Conclusion

The DIW printing technique is an innovative approach with the ability to rapidly pattern functional materials over a wide range of substrates without nozzle clogging issues. This advancement has broadened its applications in flexible electronics, including OTFT fabrication. In this work, we successfully developed an all-solution-processed low-voltage OTFT device with a channel length of 120 μm, employing the DIW deposition technique. utilization of high-k PVP dielectric enabled the fabrication of a low-voltage OTFT working at an operating voltage of less than -5 V. Noticeably, the proposed BGBC TIPS-pentacene OTFT device exhibited  $\mu$ sat of  $4.49 \times 10^{-1}$ cm<sup>2</sup>/Vs, Vth of -1.5 V,  $I_{ON}/I_{OFF}$  of up to 108 (at  $V_{G}$ = -5 V and  $V_D = -2.5 \text{ V}$ ), and S of 66.8 mV/decade. Interestingly, the overall processing temperature was kept below 150 °C to ensure compatibility with flexible electronics requirements. A comprehensive scalability study focusing on channel length variations could provide critical insights into optimizing processing conditions, improving device uniformity, and reducing material costs, making DIW printing a viable option for large-scale OTFT production. Optimizing channel lengths is particularly important as it directly affects charge carrier mobility, threshold voltage, and switching speed, and successful scalability could enable cost-effective OTFT deployment in flexible electronics and wearable devices.

#### Ackonwledgment

The authors would like to express gratitude to USM School of Electrical and Electronic Engineering Semiconductor Laboratory (SEEE Semiconductor Lab) and USM School of Materials and Mineral Resources Engineering Electronic Laboratory for the research facilities to conduct the research.

#### Funding

This work was supported by a publication incentive grant from Universiti Malaysia Perlis (UmiMAP) and the Ministry of Higher Education Malaysia for the Fundamental Research Grant Scheme with Project code: FRGS/1/2020/TK0/USM/02/30.

#### **Authors contributions**

Data underlying the results presented in this paper are available from the corresponding author upon reasonable request.

#### Availability of data and materials

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Conflict of interests**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### References

- [1] N. S. Yusof, M. F. P. Mohamed, N. A. Ghazali, M. F. A. J. Khan, S. Shaari, and M. N. Mohtar. "Evolution of solution-based organic thin-film transistor for healthcare monitoring- from device to circuit integration: A review.". 61(12):11405-11431, 2022. DOI: https://doi.org/10.1016/j.aej.2022.05.013.

- [2] H. J. Kwon et al. "Molecular engineering of printed semiconducting blends to develop organic integrated circuits: Crystallization,  ${\bf charge\ transport,\ and\ device\ application\ analyses.}".\ {\it ACS\ Applied}$ Materials & Interfaces, 14(20):23678-23691, 2022. DOI: https://doi.org/10.1021/acsami.2c02032.

- [3] N. Lago, M. Buonomo, F. Prescimone, S. Toffanin, M. Muccini, and A. Cester. "Direct comparison of the effect of processing conditions in electrolyte-gated and bottom-gated TIPS-pentacene transistors.". Electronic Materials, 3(4):281-290, 2022. DOI: https://doi.org/10.3390/electronicmat3040024.

- [4] Y. Shi, J. Liu, Y. Hu, W. Hu, and L. Jiang. "Effect of contact resistance in organic field-effect transistors.". Nano Select, 2(9): 1661-1681, 2021. DOI: https://doi.org/10.1002/nano.202000059.

- [5] N. Mohammadian and L. A. Majewski. "High capacitance dielectrics for low voltage operated OTFTs.". IntechOpen, 2020. DOI: https://doi.org/10.5772/intechopen.91772

- [6] S. Kim, J. Seo, J. Choi, and H. Yoo. "Vertically integrated electronics: New opportunities from emerging materials and devices.". Nano-Micro Letters, 14:201, 2022. DOI: https://doi.org/10.1007/s40820-022-00942-1.

- [7] J. Choi and H. Yoo. "Combination of polymer gate dielectric and two-dimensional semiconductor for emerging field-effect transistors.". Polymers, 15(6):1395, 2023. DOI: https://doi.org/10.3390/polym15061395.

- [8] W. Tang, L. Feng, J. Zhao, Q. Cui, S. Chen, and X. Guo. "Inkjet printed fine silver electrodes for all-solution-processed lowvoltage organic thin film transistors.". Journal of Materials Chemistry C, 2(11):1995-2000, 2014. DOI: https://doi.org/10.1039/C3TC32134G.

- [9] R. Tao, H. Ning, J. Chen, J. Zou, Z. Fang, and C. Yang. "Inkjet printed electrodes in thin film transistors.". IEEE Journal of Electron Device Society, 6:774-790, 2018. DOI: https://doi.org/10.1109/JEDS.2018.2852288.

- [10] R. S. Massey, X. Song, and R. Prakash. "Direct printed flexible organic thin-film transistors with cross-linked PVA-carrageenan gate dielectric.". IEEE Sensors Letters, 7(5):4500804, 2023. DOI: https://doi.org/10.1109/LSENS.2023.3271061.

- [11] A. Martinelli, A. Nitti, R. Po, and D. Pasini. "3D Printing of layered structures of metal-ionic polymers: recent progress, challenges and opportunities.". Materials, 16(15):5327, 2023. DOI: https://doi.org/10.3390/ma16155327.

- [12] N. S. Yusof, M. F. P. Mohamed, N. A. Ghazali, M. F. A. J. Khan, M. Z. Pakhuruddin, and S. Shaari. "All solution processable OTFT-based on direct-written printing method towards flexible electronics applications.". Journal of Advanced Research in Applied Sciences

- and Engineering Technology, 41(2):93-101, 2024. DOI: https://doi.org/10.37934/araset.41.2.93101.

- [13] N. S. Yusof, M. F. P. Mohamed, N. A. Ghazali, M. K. Ishak, and S. Shaari, "Direct-written silver electrodes for all-solutionprocessed low-voltage organic thin film transistors towards flexible electronics applications.". Journal of Advanced Research in Micro and Nano Engineering, 21(1):75-88, 2024. DOI: https://doi.org/10.37934/armne.21.1.7588.

- [14] Z. Hou, H. Lu, Y. Li, L. Yang, and Y. Gao. "Direct ink writing of materials for electronics-related applications: A mini review.". Frontiers in Materials, 8:647229, 2021. DOI: https://doi.org/10.3389/fmats.2021.647229.

- [15] J. P. Hong, A. Y. Park, S. Lee, J. Kang, N. Shin, and D. Y. Yoon. "Tuning of Ag work functions by self-assembled monolayers of aromatic thiols for an efficient hole injection for solution processed triisopropylsilylethynyl pentacene organic thin film transistors.". Applied Physics Letters, 92(14):143311, 2008. DOI: https://doi.org/10.1063/1.2907691.

- [16] S. Conti, S. Lai, P. Cosseddu, and A. Bonfiglio. "An inkjet-printed, ultralow voltage, flexible organic field effect transistor.". Materials Technologies, 2(2):1600212, 2017. DOI: https://doi.org/10.1002/admt.201600212.

- [17] K. Gooden, Amrit Laudari, G. Knotts, and S. Guha. "Printed dielectric-based organic diodes and transistors.". Flexible and Printed Electronics, 1:05004, 2016. DOI: https://doi.org/10.13140/RG.2.1.3037.6080.

- [18] A. K. Mahato, D. Bharti, P. Saxena, V. Raghuwanshi, I. Varun, and S. P. Tiwari. "Influence of molecular weight of polymer dielectric on the photo-response of solution-processed OFETs.". Polymer, 14: 2021, 14:123724, 2021, DOI: https://doi.org/10.1016/j.polymer.2021.123724.

- [19] S. Y. Cho, J. M. Ko, J. Lim, J. Y. Lee, and C. Lee. "Inkjet-printed organic thin film transistors based on TIPS pentacene with insulating polymers.". Journal of Materials Chemistry C, 1(5):914–923, DOI: https://doi.org/10.1039/C2TC00360K.

- [20] S. Wageh, W. Boukhili, A. S. Alshammari, and A. Al-Ghamdi. "Experiment study and analytical modeling of fully solution processed organic thin film transistors with conductive polymer top-gate electrode: Performance optimization.". Materials Science in Semiconductor Processing, 157:107325, 2023. DOI: https://doi.org/10.1016/j.mssp.2023.107325.

- [21] Z. Zhang, Z. He, S. Bi, and K. Asare-Yeboah. "Phase segregation controlled semiconductor crystallization for organic thin film transistors.". Journal of Science: Advanced Materials and Devices, 5(2):151-163, 2020. DOI: https://doi.org/10.1016/j.jsamd.2020.05.004.

- [22] S. Jakher and R. Yadav. "Organic thin film transistor review based on their structures, materials, performance parameters, operating principle, and applications.". Microelectronic Engineering, 290:112193, 2024. DOI: https://doi.org/10.1016/j.mee.2024.112193.

- [23] M. Geiger et al. "Effect of the degree of the gate-dielectric surface roughness on the performance of bottom-gate organic thin-film transistors.". Advanced Materials Interfaces, 7(10):1902145, 2020. DOI: https://doi.org/10.1002/admi.201902145.

- [24] A. Demir, S. Bağci, S. E. San, and Z. Doğruyol. "Pentacene-based organic thin film transistor with SiO2 gate dielectric.". Surface Reviews and Letters, 22(3):1550038, 2015. DOI: https://doi.org/10.1142/S0218625X15500389.

- [25] C. C. Hung and Y. J. Lin. "Effects of (NH<sub>4</sub>)2Sx treatment on the surface properties of SiO<sub>2</sub> as a gate dielectric for pentacene thin-film transistor applications.". Materials Research Express, 5: 015101, 2018. DOI: https://doi.org/10.1088/2053-1591/aaa09d.

- [26] A. Verma, V. N. Mishra, and R. Prakash. "A self-aligned, solutionprocessed low-voltage operated organic thin-film transistor for ammonia gas sensing at room temperature.". IEEE Sensors Journal, 23(6):5561-5568, 2023.

- DOI: https://doi.org/10.1109/JSEN.2023.3236438.

- [27] L. Feng, W. Tang, X. Xu, Q. Cui, and X. Guo. "Ultralow-voltage solution-processed organic transistors with small gate dielectric **capacitance**.". *IEEE Electron Device Letters*, 34(1):129–131, 2013. DOI: https://doi.org/10.1109/LED.2012.2227236.